সুচিপত্র:

- লেখক John Day day@howwhatproduce.com.

- Public 2024-01-30 07:56.

- সর্বশেষ পরিবর্তিত 2025-01-23 14:36.

জেডিএম একটি জনপ্রিয় পিআইসি প্রোগ্রামার কারণ এটি একটি সিরিয়াল পোর্ট ব্যবহার করে, সর্বনিম্ন উপাদান এবং বিদ্যুৎ সরবরাহের প্রয়োজন হয় না। কিন্তু সেখানে বিভ্রান্তি রয়েছে, নেটে অনেক প্রোগ্রামার বৈচিত্র রয়েছে, কোনটি কোন PIC এর সাথে কাজ করে? এই "নির্দেশযোগ্য" তে আমরা JDM পরীক্ষা করেছিলাম এবং আমি দেখিয়েছিলাম কিভাবে স্পাইস ব্যবহার করে সার্কিটকে অনুকরণ করা যায় যা আপনার সমস্ত প্রশ্নের উত্তর দেবে!

সরবরাহ

LTspice যা এনালগ ডিভাইস থেকে ডাউনলোড করা যাবে এখানে।

আপনার এখানে JDM সার্কিট ফাইলও দরকার।

ধাপ 1: সিরিয়াল পোর্টের প্রয়োজনীয়তা

JDM এর জন্য একটি সিরিয়াল পোর্ট মিটিং EIA232 স্পেসিফিকেশন প্রয়োজন, আদর্শভাবে +12/-12 ভোল্টেজ লেভেলের সাথে।

টেক্সাস ইন্সট্রুমেন্টস লাইন ড্রাইভার MC1488 ডেটশীট অনুযায়ী (চিত্র 3)

আউটপুট প্রতিবন্ধকতা = 4V/8mA = 500 ohm

শর্ট সার্কিট বর্তমান সীমা = 12mV, কোন সময় সীমা ছাড়াই - চিপের কোন ক্ষতি নেই।

লাইন রিসিভারের ইনপুট প্রতিবন্ধকতা = 3k থেকে 7k ohm প্রস্তাবিত।

পুরোনো ডেস্কটপ পিসিতে সিরিয়াল পোর্টগুলি +12v/-12V ব্যবহার করে এই প্রয়োজন পূরণ করে।

নতুন ল্যাপটপ পিসিতে সিরিয়াল পোর্টগুলি কম ভোল্টেজ ব্যবহার করে। জেডিএম কাজ করতে পারে বা নাও করতে পারে - উত্তরটি আরও জটিল।

ধাপ 2: পিআইসি প্রোগ্রামিং প্রয়োজনীয়তা

পিআইসি প্রোগ্রামিং প্রয়োজনীয়তা সম্পর্কিত তথ্য মাইক্রোচিপ থেকে প্রাপ্ত। উপরের একটি সাধারণ ডিভাইসের জন্য।

ধাপ 3: JDM স্পেসিফিকেশন

আসল জেডিএম ওয়েব সাইট কি সময়ের কুয়াশায় হারিয়ে গেছে? এটি আমাদের অনুমান করতে দেয় যে ডিজাইনার মূলত স্পেসিফিকেশনের জন্য কী চেয়েছিলেন।

- VDD = 5V প্রদান করুন, এবং সর্বোচ্চ IDD = 2mA পর্যন্ত ("সকেটে" সংস্করণের জন্য)

- VHH = 13V প্রদান করুন, এবং সর্বোচ্চ IHH = 0.2mA পর্যন্ত।

- MCLR রাইজ টাইম tVHHR = 1uS max।

- ICSP সংস্করণটি লক্ষ্যমাত্রায় 22k পুল-আপের বিপরীতে MCLR কম টানতে সক্ষম হবে।

ধাপ 4: সার্কিট বর্ণনা

চিত্র JDM1 PICPgm ওয়েব সাইট থেকে নেওয়া "স্ট্যান্ডার্ড" JDM সার্কিটের উপর ভিত্তি করে। এটি হল "PIC in Socket" প্রোগ্রামার যেখানে PIC TX এবং RTS পিন থেকে শক্তি গ্রহণ করে। মূল ডায়াগ্রামটি বোঝা কঠিন ছিল তাই আমি উপরে থেকে নীচে বর্তমান প্রবাহের স্বাভাবিক কনভেনশন ব্যবহার করে এটি পুনরায় অঙ্কন করেছি। এবং আমি LED নির্দেশক "RESET", "PROG" এবং "RTS" যোগ করেছি যা নির্মাণ এবং পরীক্ষার সময় প্রয়োজনীয়। আশা করি এগুলো আচরণে কোন ক্ষতিকর প্রভাব ফেলবে না।

সার্কিট ডিজাইনের স্বাভাবিক কনভেনশন হল সমস্ত ভিত্তি সাধারণ, কিন্তু JDM এর মূল বৈশিষ্ট্য হল সিরিয়াল পোর্ট গ্রাউন্ড (GND) VDD এর সাথে সংযুক্ত। এটি বিভ্রান্তি সৃষ্টি করে কারণ সিরিয়াল পোর্ট সিগন্যালগুলি GND, PIC সিগন্যালকে লজিক গ্রাউন্ডের (VSS) সাপেক্ষে পরিমাপ করা হয়।

যখন TX উচ্চতর হয়, Q1 দুটি ফরওয়ার্ড বায়াসড ডায়োড হিসাবে আচরণ করে। (Q1 সংগ্রাহক স্বাভাবিক ট্রানজিস্টার অপারেশনের মতো বিপরীত পক্ষপাতদুষ্ট নয়)। Q1 কালেক্টর C2 চার্জ করে, যা জেনার (D3) দ্বারা VDD+8V এ আটকানো হয়। Q1 emitter প্রোগ্রাম/ভেরিফাই মোডের জন্য MCLR- এ 13V প্রদান করে।

যখন TX এটি কম হয়, ক্যাপাসিটর C3 D1 এর মাধ্যমে চার্জ করা হয় এবং VSS VDD-5V এ জেনার (D5) দ্বারা আটকানো হয়। এছাড়াও TX D1 দ্বারা (VSS-0.6) এ আটকানো হয়। Q1 বন্ধ, পরবর্তী প্রোগ্রামিং পালসের জন্য C1 তার চার্জ ধারণ করে। MCLR 0V এ D2 দ্বারা আটকানো হয়েছে, তাই PIC এখন পুনরায় সেট করা হয়েছে।

যখন আরটিএস বেশি হয়, তখন ঘড়িটি পিজিসিতে প্রেরণ করা হয়। ভিডিডি লজিক হাই -তে ডি 4 ক্ল্যাম্প পিজিসি। যখন RTS কম থাকে, তখন ক্যাপাসিটর C3 D6 এর মাধ্যমে চার্জ করা হয় এবং VSS কে VDD-5V এ জেনার (D5) দ্বারা আটকানো হয়। D6 VSS বা লজিক 0 এ PGC কে আটকায়।

প্রোগ্রামিং চলাকালীন, DTR- এ পাঠানো ডেটা PGD তে পড়ে, যা PIC ইনপুট হিসেবে কনফিগার করে। যখন DTR বেশি হয়, Q2 "emitter follower" হিসেবে কাজ করে এবং PGD ভোল্টেজ প্রায় (VDD-0.6) বা যুক্তি 1। Q2 PGD কম টানছে, যা D7 দ্বারা VSS বা লজিক 0 এ আটকানো আছে।

যাচাই করার সময় PIC সিরিয়াল পোর্টে ডেটা পাঠানোর জন্য PGD কে আউটপুট হিসেবে কনফিগার করে। ডিটিআর অবশ্যই উঁচুতে সেট করা উচিত, এবং সিটিএস -এ ডেটা পড়া হয়। যখন PGD আউটপুট বেশি হয়, Q2 বন্ধ থাকে, CTS = DTR = +12V। যখন PGD আউটপুট কম থাকে, Q2 চালু থাকে। Q2 সংগ্রাহক DTR থেকে কারেন্ট (12V+5V)/(1k+1k5) = 7mA আঁকেন এবং CTS কম করে VSS এ টানেন।

ধাপ 5: সিমুলেশনের জন্য প্রস্তুত করুন

LT মশলা ডাউনলোড করুন, এখানে প্রদত্ত সার্কিট ফাইলগুলি (*.asc) সংরক্ষণ করুন এবং খুলুন। সার্কিট অনুকরণ করার জন্য, আমাদের অবশ্যই কিছু ইনপুট দিতে হবে, তারপর আউটপুটগুলিকে "ট্রেস" করতে হবে। V1, V2 V3 আউটপুট প্রতিবন্ধক R11, R12, R13 সহ 12V সিরিয়াল পোর্ট অনুকরণ করে।

- V1 TX- এ 0.5 প্রোগ্রাম থেকে 4.5ms পর্যন্ত 2 টি প্রোগ্রাম ডাল তৈরি করে

- V2 1.5 থেকে 4.5ms পর্যন্ত DTR- এ ডেটা ডাল ফেটে উৎপন্ন করে

- V3 0.5 থেকে 3.5ms পর্যন্ত RTS- এ ঘড়ির ডালের বিস্ফোরণ তৈরি করে

উপাদান V4, X1, R15 এবং R16 সব সিমুলেশনের অংশ।

- V4 ডেটা যাচাই করার জন্য 2.5 থেকে 4.5ms পর্যন্ত 2 ডাল উৎপন্ন করে।

- জাম্পার এক্স 1 পিজিডিতে আউটপুট অনুকরণ করে।

- R15, R16 VDD এবং MCLR- এ PIC- এর "লোডিং" অনুকরণ করে।

ধাপ 6: ICSP এর জন্য পরিবর্তন

চিত্র JDM3 "সার্কিট" প্রোগ্রামিং এর সংস্করণ দেখায়। মূল থেকে পরিবর্তন হয়

- আইসিএসপি সংযোগকারীর সাথে জিআইএফ সকেট প্রতিস্থাপন করুন।

- PIC এখন সাপ্লাই টু টার্গেট সার্কিট (V5) দ্বারা চালিত।

- 5V জেনার (D5) সরান।

- ছোট 100pF ক্যাপাসিটর (C4) টার্গেট সার্কিটে PIC এর পাশে সরানো হয়।

- এলইডি যেখানে সম্ভব সার্কিট বোর্ড থেকে শক্তি গ্রহণ করে।

- টার্গেট সার্কিটে MCLR পুল-আপ রেজিস্টার (R10) এবং ডায়োড (D10) প্রয়োজন।

- সতর্কতা। টার্গেট বোর্ডের অবশ্যই একটি "ভাসমান" সরবরাহ থাকতে হবে, আদর্শভাবে একটি ব্যাটারি।

- JDM এর সাথে একই সময়ে অন্য কোন কম্পিউটার পোর্ট সংযুক্ত করে টার্গেট গ্রাউন্ড (VSS) কে কম্পিউটার/পিসি গ্রাউন্ডের সাথে সংযুক্ত করবেন না।

JDM1 সিমুলেট করার পর, C2 তে দীর্ঘ সময় চার্জের সমস্যা স্পষ্ট হয়ে ওঠে। তারপর ফ্রুটেনবোয়েল পড়ার পর দেখা যাচ্ছে যে C2 এবং Q1 আসলটিতে একটি পরিবর্তন হিসাবে যোগ করা হয়েছিল। আমি ভাবতে পারি না যে C2 এবং Q1 সমস্যা তৈরি করা ছাড়াও কী করার উদ্দেশ্যে। সুতরাং JDM4 এর জন্য, আমরা ফ্রুটেনবোয়েলের পুরানো নকশায় ফিরে যাই যা বোঝার জন্য সহজ এবং সহজবোধ্য। VSS এবং VDD+8V এর মধ্যে D1 এবং D3/LED2 ক্ল্যাম্প MCLR। R1 এর মান কমিয়ে 3k3 করা হয়েছে, 12V এ LED2 আলোকিত করার জন্য যথেষ্ট।

JDM4 দুর্বল সিরিয়াল পোর্টগুলির সাথে কাজ করার জন্য ডিজাইন করা হয়েছে। যখন TX উচ্চ (+9V), TX বর্তমান উৎস = (9-8)/(1k +3k3) = 0.2ma, শুধুমাত্র MCLR উচ্চ টানতে যথেষ্ট যদিও LED2 আলোকিত করার জন্য অপর্যাপ্ত। যখন TX কম যায় (প্রায় -7V), TX বর্তমান ডুব = (9-7)/1k = 2mA। LED1 বর্তমান = (নেতৃত্বের জন্য 7-2)/(2k7) = 1.8mA। MCLR নিচে টান বর্তমান = 7-5.5/3k3 = 0.5mA।

এই সার্কিটটিও পরীক্ষা করা হয়েছে (JDM5 সিমুলেশন) সিরিয়াল পোর্ট +/- 7V ন্যূনতম, যেখানে VHH = 13V টিকিয়ে রাখার জন্য অপর্যাপ্ত ভোল্টেজের সাথে কী ঘটে তা দেখার জন্য। C1 এর উদ্দেশ্য এখন স্পষ্ট হয়ে উঠেছে, C1 MCLR- এ একটি সংক্ষিপ্ত +উদ্দীপনা তৈরি করে, TX- এর ক্রমবর্ধমান প্রান্তে 33us স্পাইক, PIC- এর জন্য যথেষ্ট দীর্ঘ প্রোগ্রামিং মোডে প্রবেশ করার জন্য, সম্ভবত? কিন্তু জাম্পার X2 (LED1 নিষ্ক্রিয় করুন) অপসারণ করুন কারণ MCLR কম টানতে এবং LED1 একসাথে আলোকিত করার জন্য অপর্যাপ্ত কারেন্ট রয়েছে। যখন TX কম হয়ে যায়, TX কারেন্ট ডুবে যায়

ধাপ 7: সিমুলেশন ফলাফল

গ্রাফিক ফাইলগুলি দেখতে, নীচের লিঙ্কগুলিতে ডান ক্লিক করা ভাল, তারপরে "নতুন ট্যাবে লিঙ্ক খুলুন" নির্বাচন করুন

সিমুলেশন 1: আসল জেডিএম 1 এর জন্য এমসিএলআর, ভিএসএস এবং আরটিএসের সন্ধান। অবিলম্বে পর্যবেক্ষণ 1, 2 এবং 3 স্পষ্ট।

সিমুলেশন 2: এমসিএলআর এবং ভিএসএসের ট্রেস, এবং সংশোধিত জেডিএম 2 এর জন্য আরটিএস, যা পূর্ববর্তী সমস্যার সমাধান করে।

সিমুলেশন 3: JDM2 এর প্রোগ্রাম মোডে ডেটা পাঠানোর জন্য PGD, VSS এবং PGC এর ট্রেস। 3.5mS এ পর্যবেক্ষণ 4।

সিমুলেশন 4: ভেরিফাই মোডে JDM2 এর জন্য PGD, VSS এবং CTS এর ট্রেস (জাম্পার X1)োকানো হয়েছে)। ঠিক আছে

সিমুলেশন 5: JDM3 এর জন্য MCLR, VSS, PGD এবং PGC এর ট্রেস। ICSP সার্কিট থেকে শক্তি ব্যবহার করে অনেক সমস্যার সমাধান করে।

সিমুলেশন 6: +/- 9V সিরিয়াল পোর্টের সাথে JDM4 এর জন্য MCLR, VSS, PGD এবং PGC এর ট্রেস। MCLR অবিলম্বে বৃদ্ধি পায়, সম্পূর্ণরূপে কাজ করে।

সিমুলেশন 7: JDM5 এর জন্য MCLR, VSS, এবং TX এর ট্রেস +/- 7V সিরিয়াল পোর্ট এবং জাম্পার X2 সরানো হয়েছে। C1 MCLR এর ক্রমবর্ধমান প্রান্তে একটি +ve বুস্ট (স্পাইক) তৈরি করে, যা MCLR কে TX এর উপরে 13V এর দিকে ঠেলে দেওয়ার জন্য যথেষ্ট।

ধাপ 8: উপসংহার

সার্কিট অপারেশনের "গোপন রহস্য" প্রকাশে স্পাইস সত্যিই ভাল। স্পষ্টতই জেডিএম সার্কিট কাজ করে এবং অনেক পিআইসি চিপের সাথে সামঞ্জস্যপূর্ণ, কিন্তু নিম্নলিখিত পর্যবেক্ষণগুলি সম্ভাব্য সীমাবদ্ধতা/সামঞ্জস্যের সমস্যা/ত্রুটিগুলি প্রকাশ করে?

- MCLR- এর দীর্ঘ উত্থানের সময় যখন C2 VPP- কে TX- এর প্রথম পালসে চার্জ করে। স্পেসিফিকেশন ব্যর্থ 3।

- সিরিয়াল পোর্ট C2 চার্জ করে যখন TX বেশি যায় এবং RTS কম যায়। কিন্তু C3 চার্জ করার কাজটিও RTS এর। যখন উভয় একই সময়ে ঘটে তখন এটি আরটিএস -এ আরও লোড তৈরি করে, ফলস্বরূপ C3 সিমুলেশনে 2ms এ চার্জ হারায় (VSS রাইজ)। স্পেসিফিকেশন ব্যর্থ 1।

- ঘড়ি ডাল 3.5ms এ থামার পর C3 চার্জ হারায় (VSS বৃদ্ধি পেতে শুরু করে)।

- C2 এর উদ্দেশ্য কি, এটা কি আদৌ প্রয়োজন?

সমাধান

- সম্ভবত PICPgm একটি সফটওয়্যার "ওয়ার্ক-রাউন্ড" ব্যবহার করে। এটি অবশ্যই একটি দীর্ঘ TX পালস C2 তে প্রিচার্জ করতে হবে, তারপর শুধুমাত্র দ্বিতীয় TX পালসের পরে প্রোগ্রামিং মোডে প্রবেশ করবে? সিমুলেশনের জন্য আমি C2 এর মান 1uF কমিয়ে 1ms এর বৃদ্ধি সময় দিই। আদর্শ সমাধান নয়।

- C2 এবং C3 বিভক্ত করুন যাতে তারা স্বাধীনভাবে চার্জ করে। JDM2, C2 এর একটি ছোট পরিবর্তন VSS এর পরিবর্তে GND- এ উল্লেখ করা হয়েছে।

- JDM3 দ্বারা সমাধান করা হয়েছে। ICSP অনেক বেশি নির্ভরযোগ্য কারণ PIC টার্গেট সার্কিট দ্বারা চালিত।

- JDM4 সমস্যা 1 সমাধান করে।

ধাপ 9: এবং অবশেষে

পুডিং এর প্রমাণ খাওয়ার মধ্যে। এই জেডিএম কাজ করে তাই এটি ব্যবহার চালিয়ে যান।

এবং আমার সুপারিশ হল:

- সকেট প্রোগ্রামিং এবং 12V সিরিয়াল পোর্টের জন্য JDM2 ব্যবহার করুন,

- ICSP প্রোগ্রামার এবং +/- 9V এর উপরে সিরিয়াল পোর্টের জন্য JDM4 ব্যবহার করুন,

- +/- 7V এর উপরে সিরিয়াল পোর্টের জন্য সরানো জাম্পার X2 সহ JDM4 ব্যবহার করুন।

তথ্যসূত্র:

এনালগ ডিভাইস এলটি মশলা

picpgm

ফ্রুটেনবোয়েল

ধাপে ধাপে আরও PIC প্রকল্প অনুসরণ করুন

প্রস্তাবিত:

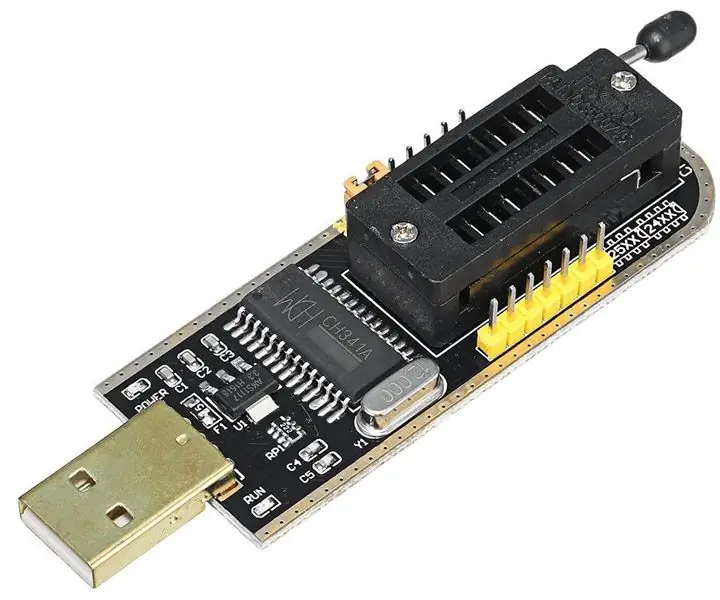

CH341A প্রোগ্রামার: 8 টি ধাপ

CH341A প্রোগ্রামার: আমি সম্প্রতি একটি CH341A মিনি প্রোগ্রামার কিনেছি। মিনি প্রোগ্রামার ঠিক আছে এবং 24 এবং 24 সিরিজের চিপ ব্যবহার করতে পারে। এটি খুব কম খরচে কিন্তু বেশ উপকারী কারণ আমি এটি ব্যবহার করে আমার কম্পিউটার BIOS এবং রাউটার ফার্মওয়্যার ফ্ল্যাশ করতে পারি। WCH দয়া করে প্রকাশ করেছে

আইএসপি হিসাবে আরডুইনো -- AVR এ হেক্স ফাইল বার্ন করুন AVR এ ফিউজ -- Arduino প্রোগ্রামার হিসাবে: 10 টি ধাপ

আইএসপি হিসাবে আরডুইনো || AVR এ হেক্স ফাইল বার্ন করুন AVR এ ফিউজ || প্রোগ্রামার হিসেবে Arduino: ……………………… আরো ভিডিও পেতে দয়া করে আমার ইউটিউব চ্যানেলে সাবস্ক্রাইব করুন …….. এই নিবন্ধটি isp হিসাবে arduino সম্পর্কে সব। আপনি যদি হেক্স ফাইল আপলোড করতে চান অথবা যদি আপনি AVR এ আপনার ফিউজ সেট করতে চান তাহলে আপনাকে কোন প্রোগ্রামার কেনার দরকার নেই, আপনি করতে পারেন

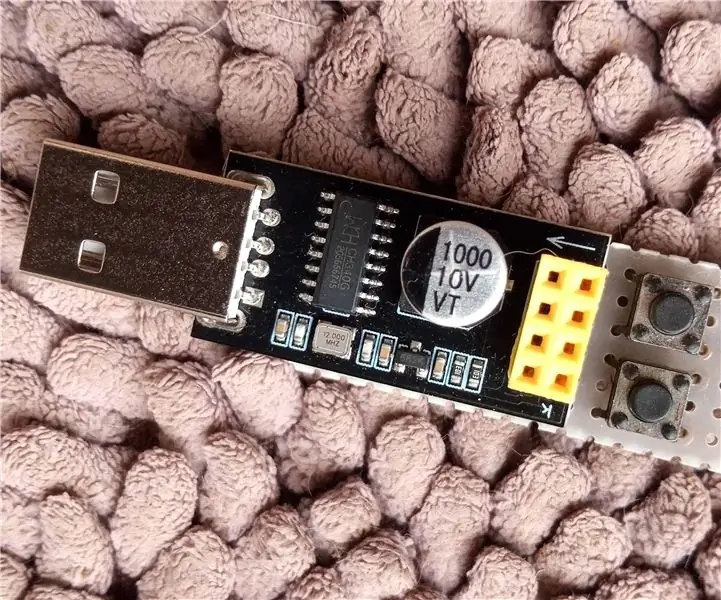

ESP -01 প্রোগ্রামার হ্যাক - সহজ এক :): 6 টি ধাপ

ESP-01 প্রোগ্রামার হ্যাক-দ্য ইজি ওয়ান :): হাই ESPers, এই নির্দেশে আমি আপনাকে ESP-01 / ESP8266-01 / ES-01 মডিউলের জন্য প্রোগ্রামার বানানোর জন্য একটি সহজ হ্যাক দেখাব। আমাদের অধিকাংশই এই মডিউলের জন্য প্রোগ্রামার হিসেবে একটি Arduino বোর্ড বা FTDI USB-TTL ডিভাইস ব্যবহার করেছেন। উভয় পদ্ধতি জরিমানা কাজ করে। কিন্তু টি

ESP8266 ফ্ল্যাশার এবং প্রোগ্রামার, IOT ওয়াইফাই মডিউল ব্যবহার করে কিভাবে ESP8266 AT ফার্মওয়্যার ফ্ল্যাশ বা প্রোগ্রাম করবেন: 6 টি ধাপ

ESP8266 ফ্ল্যাশার এবং প্রোগ্রামার, IOT ওয়াইফাই মডিউল ব্যবহার করে কিভাবে ESP8266 AT ফার্মওয়্যার ফ্ল্যাশ বা প্রোগ্রাম করবেন: বর্ণনা: এই মডিউলটি ESP8266 মডিউল ESP-01 বা ESP-01S এর জন্য একটি USB অ্যাডাপ্টার /প্রোগ্রামার। এটি ESP01 প্লাগ করার জন্য সুবিধামত 2x4P 2.54mm মহিলা হেডার দিয়ে লাগানো হয়েছে। এছাড়াও এটি 2x4P 2.54mm পুরুষ h এর মাধ্যমে ESP-01 এর সমস্ত পিন ভেঙে দেয়

সিম্বল ঘড়ি পর্যালোচনা: 6 টি ধাপ

সিম্বল ঘড়ি পুনর্বিবেচনা: আমার প্রথম সেট থেকে আমার একটি পুরানো নাস্কার ঘড়ি এবং জাঙ্ক সিম্বাল ছিল। যখন আমি একটি সিম্বাল ঘড়ি তৈরির ধারণা পেয়েছিলাম তখন তারা জায়গা নিচ্ছিল।