সুচিপত্র:

- ধাপ 1: ব্লক ডায়াগ্রাম

- পদক্ষেপ 2: অপারেশনের নীতি

- ধাপ 3: যুক্তি বাস্তবায়ন

- ধাপ 4: অচলাবস্থার সমাধান

- ধাপ 5: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 0 সার্কিট

- ধাপ 6: ডিভাইস কনফিগারেশন - SPI ক্লকিং লজিক

- ধাপ 7: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 0 উপাদান বৈশিষ্ট্য

- ধাপ 8: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 1 সার্কিট

- ধাপ 9: ডিভাইস কনফিগারেশন - 3 -বিট বাইনারি কাউন্টার

- ধাপ 10: ডিভাইস কনফিগারেশন - 3 -বিট তুলনা যুক্তি

- ধাপ 11: ডিভাইস কনফিগারেশন - ডিজিটাল তুলনা লজিক এবং অস্থায়ী রেজিস্টার

- ধাপ 12: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 1 উপাদান বৈশিষ্ট্য

- ধাপ 13: ফলাফল

- লেখক John Day day@howwhatproduce.com.

- Public 2024-01-30 07:57.

- সর্বশেষ পরিবর্তিত 2025-01-23 14:36.

কন্ট্রোল সিস্টেম এবং সংশ্লিষ্ট ডিভাইসগুলি একাধিক বিদ্যুৎ উৎসের সাথে কাজ করে, যেমন বায়াস লাইন বা ব্যাটারি, এবং অবশ্যই একটি প্রদত্ত সেটের মধ্যে সর্বোচ্চ (বা সর্বনিম্ন) লাইন ট্র্যাক করতে হবে।

উদাহরণস্বরূপ, একটি "মাল্টি ব্যাটারি" -চালিত সিস্টেমে লোড স্যুইচিংয়ের জন্য প্রয়োজন হয় যে সিস্টেমটি ব্যাটারি অ্যারের মধ্যে ন্যূনতম বা সর্বাধিক ভোল্টেজ (বিশেষ সুইচিং অ্যালগরিদমের একটি ফাংশন হিসাবে সর্বোচ্চ বা সর্বনিম্ন) পর্যবেক্ষণ করে এবং গতিশীলভাবে লোডকে রুট করে রিয়েল টাইমে সবচেয়ে উপযুক্ত উৎস। বিকল্পভাবে, সঠিক চার্জিংয়ের জন্য সিস্টেমকে সাময়িকভাবে সর্বনিম্ন-ভোল্টেজের ব্যাটারি সংযুক্ত করতে হতে পারে।

আরেকটি উদাহরণ হল আধুনিক সৌর বিদ্যুৎ ব্যবস্থা, যেখানে প্রতিটি সোলার প্যানেল টিলট্রোটেট মেকানিজম এবং সোলার ট্র্যাকিং সার্কিট দিয়ে সজ্জিত (পরবর্তীতে প্যানেলের দিকে সূর্যের অবস্থান তথ্য সরবরাহ করে)। সর্বাধিক-ভোল্টেজ তথ্যের সাথে, প্রতিটি সোলার প্যানেলের অবস্থানটি স্ট্রিং প্যানেলের ভিত্তিতে সূক্ষ্মভাবে টিউন করা যায় যা প্রকৃতপক্ষে সর্বোচ্চ আউটপুট ভোল্টেজ সরবরাহ করে, এইভাবে পাওয়ার অপ্টিমাইজেশনের একটি উচ্চতর স্তর অর্জন করে।

বাণিজ্যিক আইসি (প্রধানত মাইক্রোকন্ট্রোলার) এর বিভিন্ন ব্র্যান্ড রয়েছে যা নীতিগতভাবে একটি সর্বোচ্চ ভোল্টেজ অনুসরণকারীকে বাস্তবায়ন করতে পারে। যাইহোক, তাদের প্রোগ্রামিং প্রয়োজন এবং মিশ্র-সংকেত সমাধানের চেয়ে কম খরচে কার্যকর। একটি ডায়ালগ গ্রিনপাক design নকশা পরিপূরক নকশার সামর্থ্য, আকার এবং মডুলারিটিকে ইতিবাচকভাবে প্রভাবিত করতে পারে। এই নকশাটি একটি একক চিপে এনালগ এবং ডিজিটাল সার্কিট্রি উভয়কে সংহত করার সুবিধা কাজে লাগায়।

এই নির্দেশনায়, আটটি স্বতন্ত্র উৎসের মধ্যে একটি সর্বোচ্চ (বা শেষ পর্যন্ত মিনিট) ভোল্টেজ ফাইন্ডার বাস্তবায়নের জন্য প্রয়োজনীয় এনালগ ফ্রন্ট-এন্ড এবং ডিজিটাল লজিক প্রয়োগ করা হয়েছে।

8-চ্যানেল এনালগ সর্বোচ্চ/মিনিট ভোল্টেজ মনিটর বাস্তবায়নের জন্য একটি SLG46620G ব্যবহার করা হয়।

নীচে আমরা 8-চ্যানেল এনালগ সর্বোচ্চ/মিনিট ভোল্টেজ মনিটর তৈরির জন্য কীভাবে প্রোগ্রাম করা হয়েছে তা বোঝার জন্য প্রয়োজনীয় পদক্ষেপগুলি বর্ণনা করেছি। যাইহোক, যদি আপনি শুধু প্রোগ্রামিং এর ফলাফল পেতে চান, ইতিমধ্যে সম্পন্ন GreenPAK ডিজাইন ফাইল দেখতে GreenPAK সফটওয়্যারটি ডাউনলোড করুন। আপনার কম্পিউটারে গ্রীনপ্যাক ডেভেলপমেন্ট কিট লাগান এবং 8-চ্যানেল এনালগ সর্বোচ্চ/মিনিট ভোল্টেজ মনিটর তৈরি করতে প্রোগ্রাম হিট করুন।

ধাপ 1: ব্লক ডায়াগ্রাম

চিত্র 1 বাস্তবায়িত সিস্টেমের বৈশ্বিক চিত্র দেখায়।

8 টি ভেরিয়েবল ভোল্টেজ উত্সের একটি স্ট্রিং মাল্টিপ্লেক্সড এবং গ্রিনপাকের এডিসি মডিউলের সাথে সংযুক্ত একটি কাস্টমাইজড অভ্যন্তরীণ নকশার সাথে সংযুক্ত যা অন্যদের ক্ষেত্রে সর্বোচ্চ ভোল্টেজ সহ উৎস নির্বাচন করতে সক্ষম। অভ্যন্তরীণ যুক্তি প্রদর্শন বা আরও প্রক্রিয়াকরণের জন্য এই তথ্য আউটপুট করে।

ডিজাইনটি গ্রীনপাক এসএলজি 46620 জি পণ্যের উপর ভিত্তি করে তৈরি করা হয়েছে, কারণ এটি অ্যাপ্লিকেশনের জন্য প্রয়োজনীয় সমস্ত এনালগ এবং ডিজিটাল বিল্ডিং ব্লকগুলি সংযুক্ত করে। এই বাস্তবায়নে অ্যারেটি একটি ADG508 এনালগ মাল্টিপ্লেক্সারের মাধ্যমে সরাসরি গ্রীনপ্যাক আইসি দ্বারা চালিত হয়।

আউটপুট তথ্য হল একটি 3-বিট ডিজিটাল নম্বর যা সর্বোচ্চ ভোল্টেজের ভোল্টেজ সোর্স নম্বরের সাথে সম্পর্কিত। এই তথ্য পাওয়ার একটি সরাসরি উপায় হল 7-সেগমেন্ট ডিসপ্লের মাধ্যমে নম্বর দেখানো। SLG46620G এর ডিজিটাল আউটপুটকে 7-সেগমেন্ট ডিসপ্লে ড্রাইভার, যেমন রেফারেন্সে বর্ণিত গ্রিনপ্যাক সমাধান বা সাধারণ 74LS47 IC- এর মাধ্যমে সহজেই সম্পন্ন করা যায়।

উপস্থাপিত সার্কিট সর্বাধিক ভোল্টেজের সন্ধান করে। নকশাটিকে ন্যূনতম ভোল্টেজ ফাইন্ডারে রূপান্তর করতে, এনালগ মাল্টিপ্লেক্সার এবং গ্রিনপাক এনালগ ইনপুটের মধ্যে একটি সাধারণ প্রি-কন্ডিশনিং সার্কিট যুক্ত করতে হবে, 1 ভি রেফারেন্স ভোল্টেজ থেকে মাল্টিপ্লেক্সার আউটপুট বিয়োগ করতে হবে।

পদক্ষেপ 2: অপারেশনের নীতি

নকশাটির লক্ষ্য সর্বোচ্চ ভোল্টেজের সাথে উৎস নির্বাচন করা, অতএব শেষ-সর্বাধিক মান সংরক্ষণ করার সময় পুরো অ্যারেতে একটি স্ক্যান করা হয় এবং ইনপুটের পরবর্তী মান (যা স্ক্যানের পরবর্তী ভোল্টেজ উৎসের সাথে সম্পর্কিত) এর সাথে তুলনা করা হয়।

নিম্নলিখিতগুলিতে আমরা সমস্ত ইনপুটগুলির সাথে একটি সম্পূর্ণ মাল্টিপ্লেক্সিং ক্রমকে "স্ক্যান" বা "লুপ" হিসাবে উল্লেখ করব।

দুটি মানের মধ্যে তুলনা ACMP উপাদানগুলির মাধ্যমে সম্পন্ন করা হয় না (তবে, SLG46620G তে উপলব্ধ), বরং DCMP মডিউল দ্বারা, একবার মান যথাক্রমে ডিজিটাল করা হলে। এটি একটি উন্নত এবং পরিমার্জিত কৌশল যা প্রথমে রেফারেন্সে সম্বোধন করা হয়।

চিত্র 2 দেখায় কিভাবে এই ডিজাইনের জন্য SLG46620G গঠন করা হয়েছে।

এনালগ ইনপুট সিগন্যাল PGA কম্পোনেন্টের মাধ্যমে ADC ইনপুটে যায় 1 এর একটি সেট লাভের সাথে। GreenPAK ADC মডিউলের পরিসীমা।

এডিসি সিঙ্গেল এন্ডেড মোডে কাজ করে এবং এনালগ সিগন্যালকে 8-বিট ডিজিটাল কোডে রূপান্তরিত করে, যা পরে ডিসিএমপি মডিউলে স্থানান্তরিত হয়। ডিজিটাল কোডটি এসপিআই ব্লকেও খাওয়ানো হয়, এটি একটি এডিসি/এফএসএম বাফার হিসাবে কনফিগার করা হয়, যেখানে একটি ডিজিটাল কোড সংরক্ষণ করা যায় এবং পরবর্তী পালস এসপিআই সিএলকে ইনপুটে না আসা পর্যন্ত পরিবর্তন করা যায় না। লক্ষ্য করুন যে একটি ডেডিকেটেড লজিক ব্লক SPI CLK ইনপুট চালায়। আমরা এই অংশটি পরে তদন্ত করব, কারণ এটি সঠিক পরিচালনার জন্য দায়ী "মূল" যুক্তি। একটি নতুন ডিজিটাল কোড SPI মডিউলে সংরক্ষিত হয় শুধুমাত্র যদি এটি প্রকৃত সর্বোচ্চ ইনপুট ভোল্টেজের অন্তর্গত হয়।

DCMP কম্পোনেন্টটি বর্তমান ADC ডেটাকে শেষ বিজয়ীর সাথে তুলনা করতে ব্যবহৃত হয় (এটিই সর্বশেষ সর্বোচ্চ পাওয়া যায়) যা SPI ব্লকে সংরক্ষিত থাকে। এটি নতুন আউটপুট এ একটি পালস তৈরি করবে যখন নতুন এডিসি ডেটা আগেরটির চেয়ে বেশি হবে। আমরা নতুন বিজয়ীর সাথে SPI ব্লক আপডেট করতে OUT+ সংকেত ব্যবহার করি।

একটি বৈশ্বিক ঘড়ি সংকেত ADC রূপান্তর এবং সাধারণ সময় চালায়। একবার একটি রূপান্তর সঞ্চালিত হলে, ADC এর INT আউটপুট সিগন্যাল ডাল, ADC সমান্তরাল ডেটা আউটপুটের সাথে সময় সমন্বয় করে। আমরা 3-বিট বাইনারি কাউন্টার বাড়ানোর জন্য আইএনটি আউটপুট ব্যবহার করি, যা ম্যাট্রিক্স 1 এ ডিএফএফ দ্বারা প্রয়োগ করা হয়, যা তিনটি কারণে দরকারী:

1. কাউন্টার আউটপুট লাইনগুলি বহিরাগত এনালগ মাল্টিপ্লেক্সারকে সম্বোধন করে, এইভাবে এডিসিতে পরবর্তী ইনপুট ভোল্টেজ সরবরাহ করে;

2. স্ক্যানের সময় অস্থায়ী বিজয়ীকে সংরক্ষণ করার জন্য গণনাটি 3-বিট রেজিস্টারে (ম্যাট্রিক্স 1 এ প্রয়োগ করা হয়) জমা হয়;

3. স্ক্যান সম্পন্ন হলে দ্বিতীয় 3-বিট রেজিস্টার (ম্যাট্রিক্স 0 তে প্রয়োগ করা) আপডেট করার জন্য গণনা ডিকোড করা হয়।

ধাপ 3: যুক্তি বাস্তবায়ন

ADC মডিউল ক্রমান্বয়ে সমস্ত ইনপুট ভোল্টেজের রূপান্তরিত ডেটা প্রদান করে, একের পর এক, অনির্দিষ্টকালের জন্য। একবার মাল্টিপ্লেক্সারকে 0b111 (দশমিক 7) সম্বোধন করা হলে, কাউন্টারটি 0b000 (দশমিক 0) এ বন্ধ হয়ে যায় এইভাবে ইনপুট ভোল্টেজগুলির একটি নতুন স্ক্যান শুরু হয়।

স্ক্যানের সময়, সমান্তরাল ডেটা আউটপুট বৈধ হলে ADC INT আউটপুট সিগন্যাল তৈরি হয়। যখন এই সংকেতটি স্পন্দিত হয়, তখন এনালগ মাল্টিপ্লেক্সারকে পরবর্তী ইনপুটে স্যুইচ করতে হবে, সংশ্লিষ্ট ভোল্টেজের সাথে PGA প্রদান করতে হবে। অতএব, ADC INT আউটপুট হল চিত্র 2-এর 3-বিট বাইনারি কাউন্টারের সরাসরি ক্লকিং সিগন্যাল, যার 3-বিট সমান্তরাল আউটপুট শব্দটি সরাসরি বহিরাগত এনালগ মাল্টিপ্লেক্সার (চিত্র 1-এ "V সিলেক্ট") সম্বোধন করে।

আসুন এখন একটি উদাহরণ পড়ি যেখানে ইনপুট ভোল্টেজগুলির নিম্নলিখিত সম্পর্ক থাকার কথা রয়েছে:

a) V0 <V1 <V2

খ) V2> V3, V4

গ) V5> V2

চিত্র 3 সর্বোচ্চ সিদ্ধান্ত প্রক্রিয়াতে জড়িত প্রধান সংকেতগুলি উপস্থাপন করে।

যেহেতু ডেটা অবশেষে এসপিআই বাফার রেজিস্টারে আইএনটি ডালের সাথে সমকালীনভাবে সংযুক্ত হয়, তাই একটি তুলনা উইন্ডো বিদ্যমান যেখানে এসপিআই বাফারের সামগ্রী পরবর্তী এডিসি রূপান্তর ফলাফলের সাথে তুলনা করা হয়। এই নির্দিষ্ট সময়ের ফলে DCMP আউটপুটে OUT+ ডাল উৎপাদন হয়। এসপিআই বাফার রেজিস্টারে নতুন মান লোড করতে আমরা এই ডালগুলির সুবিধা নিতে পারি।

পূর্ববর্তী চিত্রের SPI বাফার ডেটা লাইন থেকে স্পষ্টতই, SPI রেজিস্টারে সবসময় 8 টি ইনপুটের মধ্যে সর্বাধিক মান থাকে এবং এটি শুধুমাত্র তখনই আপডেট করা হয় যখন DCMP মডিউল (DCMP- এর উল্লেখ করে) প্লটের আউটপুট+ আউটপুট লাইন, অনুপস্থিত ডাল V2 এর সাথে তুলনা না হওয়া পর্যন্ত V2 কে রেজিস্টারে আটকে রাখে)।

ধাপ 4: অচলাবস্থার সমাধান

যদি বাস্তবায়িত যুক্তি ঠিক উপরে বর্ণিত হয়, তাহলে এটা স্পষ্ট যে আমরা একটি অচলাবস্থার মধ্যে পড়ে যাব: সিস্টেমটি এসপিআই বাফার রেজিস্টারে সংরক্ষিত একটির চেয়ে বেশি ভোল্টেজ সনাক্ত করতে সক্ষম।

এই ভোল্টেজ কমে গেলে এটিও বৈধ এবং তারপর আরেকটি ইনপুট, যা এখন পর্যন্ত এর চেয়ে কম, সর্বোচ্চ হয়ে যায়: এটি কখনই সনাক্ত করা যাবে না এই চিত্রটি চিত্র 4 এ আরও ভালভাবে ব্যাখ্যা করা হয়েছে যেখানে শুধুমাত্র 3 টি ইনপুট ভোল্টেজের জন্য উপস্থিত রয়েছে নির্মলতা.

পুনরাবৃত্তির সময় 2, V3 ড্রপ এবং V1 প্রকৃত সর্বোচ্চ ভোল্টেজ। কিন্তু DCMP মডিউল একটি পালস প্রদান করে না কারণ SPI বাফার রেজিস্টারে সংরক্ষিত ডেটা (0.6 V এর সাথে সম্পর্কিত) V1 (0.4 V) এর তুলনায় বড়।

সিস্টেম তারপর একটি "পরম" সর্বোচ্চ অনুসন্ধানকারী হিসাবে আচরণ করে এবং সঠিকভাবে আউটপুট আপডেট করে না।

এই সমস্যা কাটিয়ে ওঠার একটি চমৎকার উপায় হল সিস্টেমটি যখন সকল চ্যানেলের পূর্ণ ভোট চক্র সম্পন্ন করে তখন SPI বাফার রেজিস্টারে ডেটা পুনরায় লোড করা।

প্রকৃতপক্ষে, যদি সেই ইনপুটে ভোল্টেজ এখনও সর্বোচ্চ হয়, কিছুই পরিবর্তন হয় না এবং নিয়ন্ত্রণ নিরাপদে চলে যায় (উপরে চিত্র 4 উল্লেখ করে, এটি লুপ আইটারেশন 0 এবং 1 এর ক্ষেত্রে)। অন্যদিকে, যদি সেই ইনপুটে ভোল্টেজটি সুযোগের সাথে অন্য ইনপুটের চেয়ে কম মানের হয়, তাহলে মানটি পুনরায় লোড করার ফলে DCMP মডিউলটি নতুন সর্বোচ্চ মানের সাথে তুলনা করার সময় একটি OUT+ পালস তৈরি করার সম্ভাবনা দেয় (এটি হল লুপ ইটারেশন 2 এবং 3 এর ক্ষেত্রে)।

সমস্যা কাটিয়ে ওঠার জন্য লজিক সার্কিটের একটি অংশ প্রয়োজন। এটি অবশ্যই এসপিআই কম্পোনেন্টে একটি ক্লক সিগন্যাল উৎপন্ন করবে যখন লুপটি প্রকৃত সর্বোচ্চ ইনপুটে পৌঁছাবে, এইভাবে তার আপডেট হওয়া ডেটা ওয়ার্ডটি এসপিআই বাফার রেজিস্টারে পুনরায় লোড করতে বাধ্য করবে। এটি 7.2 এবং 7.6 বিভাগে আলোচনা করা হবে।

ধাপ 5: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 0 সার্কিট

SLG46620G এর দুটি ম্যাট্রিক্স ব্লক রয়েছে, যেমন চিত্র 2 -এ দেখানো হয়েছে।

সার্কিটের উপরের অংশ হল "লুপ রেজিস্টার" যা 3 টি DFFs (DFF0, DFF1, এবং DFF2) দ্বারা উপলব্ধ। ইনপুট মাল্টিপ্লেক্সারের প্রতিটি লুপের পরে এটি 7-সেগমেন্ট ডিসপ্লে ড্রাইভারকে "বিজয়ী" এর বাইনারি নম্বর পাঠানোর পরে রিফ্রেশ করা হয়, যা শেষ স্ক্যানের সর্বোচ্চ ভোল্টেজ সহ ইনপুট। ডিএফএফ -এর ঘড়ি এবং ডেটা উভয়ই যথাক্রমে ম্যাট্রিক্স 1 -এ বাস্তবায়িত যুক্তি থেকে আসে, পোর্ট P12, P13, P14, এবং P15।

নিচের অংশ হল পিন 8 এ ইনপুট সহ এনালগ ফ্রন্ট এন্ড এবং লাভ x1 সহ PGA। ADC INT আউটপুট SPI এর ক্লকিং লজিক এবং পোর্ট P0 এর মাধ্যমে ম্যাট্রিক্স 1 উভয় দিকে যায়, যেখানে এটি বাস্তবায়িত কাউন্টারের ক্লক সিগন্যাল হিসেবে কাজ করবে।

ADC এবং SPI সমান্তরাল ডেটা আউটপুট যথাক্রমে NET11 এবং NET15 লেবেল করা হয়েছে যাতে ম্যাট্রিক্স 1 -তে DCMP কম্পোনেন্টের সাথে সংযুক্ত হতে পারে।

ধাপ 6: ডিভাইস কনফিগারেশন - SPI ক্লকিং লজিক

যেমন "লজিক ইমপ্লিমেন্টেশন" বিভাগে আগে উল্লেখ করা হয়েছে, এসপিআই বাফার রেজিস্টার প্রতিবার আপডেট করা হয় যে প্রকৃত সঞ্চিত মান এবং নতুন এডিসি রূপান্তর ডেটার মধ্যে তুলনা ডিসিএমপি আউট+ আউটপুটে একটি পালস তৈরি করে।

ADC INT আউটপুটের সাথে এই সংকেত AND-ed হলে সিগন্যাল অখণ্ডতা নিশ্চিত করা হয়। এটি কোনও স্পাইক এবং মিথ্যা ট্রিগারিং এড়ায়।

আমরা এটাও বুঝিয়ে দিয়েছি যে অচলাবস্থার পরিস্থিতি এড়াতে, এসপিআই বাফারকে অবশ্যই আপডেট করতে হবে যখন লুপটি প্রকৃত বিজয়ীর ডেটাতে পৌঁছায়।

যথাযথ এসপিআই ক্লকিংয়ের জন্য গেমটিতে তিনটি সংকেত রয়েছে:

1. ADC INT আউটপুট (LUT0-IN1)

2. DCMP আউট+ আউটপুট (LUT0-IN0 পোর্ট P10 এর মাধ্যমে)

3. কাউন্ট সমান ল্যাচ সিগন্যাল (LUT0-IN2 পোর্ট P11 এর মাধ্যমে)

প্রথম দুটি হল AND-ed এবং উভয়ই OR-ED LUT0- এ, যার বাস্তবায়ন চিত্র 6-এর মতো কনফিগার করা হয়েছে।

ধাপ 7: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 0 উপাদান বৈশিষ্ট্য

পরিসংখ্যান 7-10 ম্যাট্রিক্স 0 এর অন্তর্গত অবশিষ্ট উপাদান সম্পত্তি জানালা দেখায়।

ধাপ 8: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 1 সার্কিট

ধাপ 9: ডিভাইস কনফিগারেশন - 3 -বিট বাইনারি কাউন্টার

সার্কিটের উপরের অংশে যুক্তি উপাদান রয়েছে, প্রধানত একটি 3-বিট বাইনারি কাউন্টার যা ADC INT আউটপুট দ্বারা ক্লক করা হয়েছে, যেমনটি ইতিমধ্যে আলোচনা করা হয়েছে। এই কাউন্টারটি চিত্র 12 এ দেখানো বেশ "স্ট্যান্ডার্ড" স্কিম্যাটিক দিয়ে প্রয়োগ করা হয়েছে।

এই কাউন্টারটি ফ্লিপ-ফ্লপস DFF9, DFF10, DFF11 এবং INV1, LUT4, LUT8 এর মাধ্যমে আমাদের নকশায় উপলব্ধি করা হয়েছে। DFF9 আউটপুট হল LSB এবং DFF11 হল MSB যেমন চিত্র 13 এ দেখানো হয়েছে।

LUT4 একটি XOR হিসাবে কনফিগার করা হয় যখন LUT8 চিত্র 12 এর AND-XOR যুক্তি সম্পাদন করে।

বহিরাগত এনালগ মাল্টিপ্লেক্সারকে সম্বোধন করতে কাউন্টার আউটপুট তিনটি ডিজিটাল আউটপুট পিনে যায়।

LUT10 কাউন্টারের কোড ডিকোড করে যখন একটি স্ক্যান সম্পন্ন হয় এবং DLY8 এবং P12 পোর্ট এর মাধ্যমে ম্যাট্রিক্স 0 এ একটি পালস খাওয়ায়। এটি কেবল কাউন্টারের আউটপুটগুলিকে AND-ing দ্বারা সম্পন্ন করা হয়, এইভাবে 7 ডিসেম্বর (0b111 বাইনারি, লুপের শেষ) ডিকোডিং।

ধাপ 10: ডিভাইস কনফিগারেশন - 3 -বিট তুলনা যুক্তি

চিত্র 15 বর্তমান "বিজয়ী" ঠিকানায় যখন লুপটি পুনরাবৃত্তি করছে তা সনাক্ত করতে ব্যবহৃত সার্কিটটি দেখায়। এই ক্ষেত্রে, যেমনটি ইতিমধ্যে আলোচনা করা হয়েছে, একটি সম্ভাব্য অচলাবস্থার পরিস্থিতি সমাধানের জন্য একটি ডিজিটাল পালসকে বর্তমান এডিসি ফলাফল পুনরায় লোড করতে বাধ্য করা উচিত।

"বিজয়ী" ঠিকানাটি ম্যাট্রিক্স 1 এর অস্থায়ী রেজিস্টারে সংরক্ষণ করা হয় (নীচে দেখুন), যখন বর্তমান ঠিকানাটি বাইনারি কাউন্টার দ্বারা আউটপুট হয়।

উভয় ইনপুট সমান হলে XNOR গেটস একটি সত্য (যুক্তি 1 বা 'উচ্চ') আউটপুট প্রদান করে। এবং সমস্ত বিটের জন্য এই সংকেত (LUT9) আমাদের একটি পালস দেয় যখন উভয় বাইনারি কোড একই। প্যারিটি চেকার হিসেবে XOR গেটস সম্পর্কে বিস্তারিত তথ্য রেফারেন্সে পাওয়া যাবে।

'কাউন্টার-ইকুয়েলস-ল্যাচ' সিগন্যালটি পোর্ট P11 এর মাধ্যমে ম্যাট্রিক্স 0-এ প্রেরণ করা হয়।

ধাপ 11: ডিভাইস কনফিগারেশন - ডিজিটাল তুলনা লজিক এবং অস্থায়ী রেজিস্টার

চিত্র 11 এর নিচের অংশ (চিত্র 16 এ হাইলাইট করা) ডিসিএমপি ব্লক দেখায়, এই নকশার সিদ্ধান্ত গ্রহণকারী অংশ।

DFF6, 7, এবং 8 লুপ চলাকালীন অস্থায়ী ইনপুট নম্বর "বিজয়ী" সংরক্ষণ করার জন্য একটি 3-বিট রেজিস্টার গঠন করে। ফ্লিপ-ফ্লপগুলিতে ইনপুট হল 3-বিট বাইনারি কাউন্টার আউটপুট, যেমন চিত্র 11 এর গ্লোবাল ম্যাট্রিক্স 1 সার্কিটে দৃশ্যমান, এখানে স্বচ্ছতার জন্য বাদ দেওয়া হয়েছে।

এই রেজিস্টারের আউটপুটগুলি সরাসরি 7-সেগমেন্ট ডিসপ্লে চালাতে পারে না কারণ এখানে সঞ্চিত মান স্ক্যানের সময় পরিবর্তিত হয় এবং শুধুমাত্র স্ক্যানের শেষে 'বৈধ' বলে বিবেচিত হওয়া উচিত।

এই কারণে, অস্থায়ী রেজিস্টার আউটপুটগুলি ম্যাট্রিক্স 0 এর লুপ রেজিস্টারের সাথে ইন্টার-ম্যাট্রিক্স পোর্ট P13, P14, এবং P15 এর মাধ্যমে সংযুক্ত হয়।

চিত্র 16 এ পর্যবেক্ষণ করা গুরুত্বপূর্ণ যে অস্থায়ী রেজিস্টারটি DCMP OUT+ আউটপুট দ্বারা ক্লক করা হয় যখন ADC-SPI রেজিস্টার করে তুলনামূলক ফলাফল একটি নতুন সর্বোচ্চ পাওয়া যায়।

পোর্ট P10 এর মাধ্যমে একই OUT+ সিগন্যাল ম্যাট্রিক্স 0, SPI CLK লজিকের কাছে প্রেরণ করা হয়।

ধাপ 12: ডিভাইস কনফিগারেশন - ম্যাট্রিক্স 1 উপাদান বৈশিষ্ট্য

পরিসংখ্যান 17-19 ম্যাট্রিক্স 1 এর অন্তর্ভুক্ত সম্পত্তি সম্পত্তি জানালা দেখায়।

ধাপ 13: ফলাফল

বাস্তবায়ন পরীক্ষা করার জন্য, একটি মূল্যায়ন বোর্ড প্রোটোটাইপ তৈরি করা হয়েছে, যেখানে 8 টি এনালগ ইনপুট ভোল্টেজগুলি ট্রিমপটগুলির সাথে রোধকারী বিভাজকের একটি সিরিজ দ্বারা প্রাপ্ত হয় (যেমন চিত্র 20 এ দেখানো হয়েছে)।

মাল্টিপ্লেক্সার ব্যবহৃত একটি ADG508, একটি অংশ যা একক সরবরাহ (12 V) দিয়ে কাজ করতে পারে।

7-সেগমেন্ট ডিসপ্লে ড্রাইভার 74LS47। এটি একটি সমান্তরাল ইনপুট শব্দ ডিকোড করে এবং সরাসরি একটি সাধারণ-অ্যানোড 7-সেগমেন্ট প্রদর্শন চালায়।

মূল্যায়ন বোর্ডের একটি 2x10 রাইট-এঙ্গেল সংযোগকারী রয়েছে যা সরাসরি গ্রিনপ্যাক অ্যাডভান্সড ডেভেলপমেন্ট প্ল্যাটফর্মে প্লাগ করার জন্য তার সম্প্রসারণ সংযোগকারীতে চিত্র 21 এ দেখানো হয়েছে।

গ্রিনপ্যাক অ্যাডভান্সড ডেভেলপমেন্ট প্ল্যাটফর্মের সাথে সংমিশ্রণটি দ্রুত চেক করার জন্য সংকেতগুলির পরিমাপ গ্রহণ করা খুব সহজ করে তোলে। উদাহরণস্বরূপ, চিত্র 22 একটি এইচপি 54620A লজিক বিশ্লেষক দ্বারা ধরা সিগন্যালের একটি সেট (যথাক্রমে ক্লক, এডিসি ইনট আউটপুট এবং ডিসিএমপি আউট+ আউটপুট) দেখায়। ওয়েভফর্মগুলি OUT+ সিগন্যালের ক্রমবর্ধমান প্রান্তের দ্বারা ট্রিগার করা হয় ('A> B' হিসাবে লেবেল করা স্কোপে), তাই এনালগ ইনপুটগুলির মধ্যে একটি নতুন সর্বোচ্চ ভোল্টেজ ধরা পড়লে এটি একটি তরঙ্গাকৃতি ক্যাপচার। প্রকৃতপক্ষে, চিত্র 22 এ দেখানো সংশ্লিষ্ট ভোল্টেজ বাড়ানোর জন্য এটি মূল্যায়ন বোর্ডের একটি ট্রিমপটকে ঘোরানোর মাধ্যমে প্রাপ্ত হয়েছিল।

চিত্র 23 মূল্যায়ন বোর্ডের পরিকল্পিত দেখায়।

উপসংহার

এই নির্দেশনায়, আমরা মাল্টি-চ্যানেল কন্ট্রোল সিস্টেমে একটি সাধারণ সংযোজন হিসাবে ব্যবহার করার জন্য একটি আট-চ্যানেল সর্বোচ্চ (বা মিনিট) ভোল্টেজ ফাইন্ডার প্রয়োগ করেছি। উপস্থাপিত পদ্ধতি গ্রিনপ্যাক উপাদানগুলির উন্নত বৈশিষ্ট্যগুলি কাজে লাগায় এবং দেখায় যে কীভাবে একটি একক চিপ এনালগ এবং ডিজিটাল ফাংশনে সংহত করা সম্ভব। বেশ কয়েকটি বাণিজ্যিক আইসিকে ডায়ালগ গ্রিনপাক দিয়ে প্রতিস্থাপন করা যেতে পারে যাতে আবেদনের আকার এবং খরচ কমানো যায়।

প্রস্তাবিত:

কিভাবে একটি এনালগ পিন ব্যবহার করে একাধিক এনালগ মান পড়বেন: 6 টি ধাপ (ছবি সহ)

কিভাবে একটি এনালগ পিন ব্যবহার করে একাধিক এনালগ মান পড়বেন: এই টিউটোরিয়ালে, আমি আপনাকে দেখাব কিভাবে শুধুমাত্র একটি এনালগ ইনপুট পিন ব্যবহার করে একাধিক এনালগ মান পড়তে হয়

উচ্চ ভোল্টেজ ব্যাটারির জন্য ভোল্টেজ মনিটর: 3 টি ধাপ (ছবি সহ)

উচ্চ ভোল্টেজ ব্যাটারির জন্য ভোল্টেজ মনিটর: এই গাইডে আমি আপনাকে ব্যাখ্যা করব কিভাবে আমি আমার বৈদ্যুতিক লংবোর্ডের জন্য আমার ব্যাটারি ভোল্টেজ মনিটর তৈরি করেছি। আপনি যা চান তা মাউন্ট করুন এবং আপনার ব্যাটারিতে (Gnd এবং Vcc) মাত্র দুটি তার সংযুক্ত করুন। এই গাইডটি ধরে নিয়েছে যে আপনার ব্যাটারির ভোল্টেজ 30 ভোল্টের বেশি, w

ডিসি - ডিসি ভোল্টেজ স্টেপ ডাউন সুইচ মোড বাক ভোল্টেজ কনভার্টার (LM2576/LM2596): 4 ধাপ

ডিসি-ডিসি ভোল্টেজ স্টেপ ডাউন সুইচ মোড বক ভোল্টেজ কনভার্টার (LM2576/LM2596): একটি অত্যন্ত দক্ষ বক কনভার্টার তৈরি করা একটি কঠিন কাজ এবং এমনকি অভিজ্ঞ ইঞ্জিনিয়ারদের ডানদিকে আসার জন্য একাধিক ডিজাইনের প্রয়োজন হয়। এটি একটি ডিসি-টু-ডিসি পাওয়ার কনভার্টার, যা ভোল্টেজ নিচে নামায় (স্টেপ আপ করার সময়

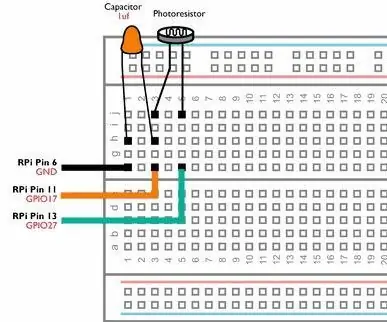

রাস্পবেরি পাই জিপিআইও সার্কিট: এডিসি ছাড়া এলডিআর এনালগ সেন্সর ব্যবহার করে (এনালগ টু ডিজিটাল কনভার্টার): 4 টি ধাপ

রাস্পবেরী পাই জিপিআইও সার্কিট: এডিসি ছাড়া এলডিআর এনালগ সেন্সর ব্যবহার করা (ডিজিটাল কনভার্টার থেকে এনালগ): আমাদের আগের নির্দেশাবলীতে, আমরা আপনাকে দেখিয়েছি কিভাবে আপনি আপনার রাস্পবেরি পাই এর জিপিআইও পিনগুলিকে এলইডি এবং সুইচগুলির সাথে সংযুক্ত করতে পারেন এবং জিপিআইও পিনগুলি কীভাবে উচ্চ হতে পারে অথবা কম। কিন্তু আপনি যদি আপনার রাস্পবেরি পাইকে এনালগ সেন্সর দিয়ে ব্যবহার করতে চান? আমরা যদি একটি ব্যবহার করতে চাই

পিক্যাক্স ভিত্তিক ডিজিটাল থার্মোমিটার সর্বোচ্চ এবং ন্যূনতম: 13 টি ধাপ

সর্বোচ্চ এবং ন্যূনতম সঙ্গে Picaxe ভিত্তিক ডিজিটাল থার্মোমিটার: (দয়া করে একটি বার্তা দিন, কিন্তু খুব সমালোচনা করবেন না, এটি আমার প্রথম নির্দেশযোগ্য !!) এটি আমাদের ক্যাম্পার-ভ্যানের জন্য তৈরি একটি থার্মোমিটার, বাইরের তাপমাত্রা দেখানোর জন্য। এটি একটি পিক্যাক্স চিপের উপর ভিত্তি করে তৈরি করা হয়েছে কারণ এগুলি সস্তা এবং ব্যবহার করা সহজ। যদি এর জন্য হয়