সুচিপত্র:

- লেখক John Day day@howwhatproduce.com.

- Public 2024-01-30 07:58.

- সর্বশেষ পরিবর্তিত 2025-01-23 14:36.

এই ieldাল দিয়ে আপনার মোজো ডেভেলপমেন্ট বোর্ডকে বাইরের ইনপুটগুলির সাথে সংযুক্ত করুন।

মোজো উন্নয়ন বোর্ড কি?

মোজো ডেভেলপমেন্ট বোর্ড হল একটি উন্নয়ন বোর্ড যা Xilinx spartan 3 FPGA এর উপর ভিত্তি করে তৈরি। বোর্ডটি আলচিত্রি দ্বারা তৈরি করা হয়েছে। এফপিজিএ খুব দরকারী যেখানে একাধিক প্রক্রিয়া একসাথে সম্পাদন করা আবশ্যক।

আপনি কি প্রয়োজন হবে?

সরবরাহ

মোজো ডেভেলপমেন্ট বোর্ড

গারবার ফাইল

8 x 15k ওহম প্রতিরোধক (*চ্ছিক*)

4 x 470 ওহম প্রতিরোধক

4 x 560 ওহম প্রতিরোধক

4 x সিসি সেগমেন্ট ডিসপ্লে

4 x 3mm LEDs

4 x SPDT স্পর্শযোগ্য সুইচ

1 x 4 পজিশন সারফেস মাউন্ট ডিআইপি সুইচ

2 x 25 বাই 2 বা 4 x 25 হেডার

1x 2 বাই 5 পিন বক্স হেড

তাতাল

ঝাল

ফ্লাক্স

*(যদি এই প্রতিরোধকগুলি বাদ দেওয়া হয় অভ্যন্তরীণ পুলআপ/পুলডাউন প্রাসঙ্গিক পিনের জন্য সক্ষম করা আবশ্যক)

ধাপ 1: আপনার পছন্দের পিসিবি প্রস্তুতকারকের কাছে গারবার আপলোড করুন

আমার বোর্ডের জন্য আমি JLC PCB থেকে অর্ডার করেছি।

আমি যে পরিবর্তনটি করেছি তা হল রঙ যা আমি মোজোর কালো রঙের সাথে মেলাতে চেয়েছিলাম।

ধাপ 2: বোর্ড সমাবেশ

সোল্ডারিং করার সময় আমি সর্বদা সর্বনিম্ন অংশগুলি সোল্ডার করার জন্য দরকারী মনে করি তাই প্রতিরোধক দিয়ে শুরু করা একটি ভাল ধারণা।

R5, R6, R7, R8, R9, R10, R11 এবং R12 হল 15k ওহম প্রতিরোধক যা সুইচগুলি নামানোর জন্য ব্যবহৃত হয় (যদি আপনি অভ্যন্তরীণ পুলআপ/পুলডাউন ব্যবহার করছেন তবে এটি উপেক্ষা করুন)।

R1, R2, R3, R4 হল 560 ওহম প্রতিরোধক যা 7 সেগমেন্ট ডিসপ্লের মাধ্যমে কারেন্ট সীমিত করার জন্য দায়ী।

R13, R14, R15, R16 হল 470 ওহম প্রতিরোধক যা 4 LED এর মাধ্যমে বর্তমানকে সীমিত করার জন্য দায়ী।

পরবর্তী সোল্ডার ডিপ সুইচ, স্পর্শকাতর সুইচ, এলইডি, সাত সেগমেন্ট ডিসপ্লে এবং বক্স হেডার সংযোগকারী সেই ক্রমে।

এখন পিনগুলি সারিবদ্ধ করতে মোজোতে 25 বাই 2 (বা 2 25 দ্বারা 1) রাখুন। পিনের সাথে ieldালটি সারিবদ্ধ করুন এবং এটি জায়গায় ঝাল করুন।

ধাপ 3: সফটওয়্যার সেটআপ

আলচিট্রি ওয়েবসাইটের উল্লেখ করা সফ্টওয়্যারের জন্য আপনাকে শুরু করতে এবং Xilinx ISE ইনস্টল করার জন্য কী প্রয়োজন তা জানাবে। যাইহোক.ucf ফাইলটি পরিবর্তন করা যাতে এটি জানতে পারে যে আপনার প্রোগ্রামটি চালানোর জন্য কোন পিনগুলি গুরুত্বপূর্ণ।

এখানে.ucf ফাইলটি আমি withালের সাথে ব্যবহার করি:

কনফিগ VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIOD "clk" 50 MHz HIGH 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

মনে রাখবেন যদি আপনি.ucf এর মধ্যে পিনগুলি সম্পাদনা করতে পুলডাউন প্রতিরোধক ইনস্টল না করেন

| চূর্ণ করা; o

| পুলপ;

আপনি যদি কোন কিছুর জন্য ব্লক ব্যবহার করতে চান তাহলে সংযোগগুলি নিম্নরূপ। ব্লক পিন নম্বরটি বাম এবং ডান মোজো পিন নম্বর যা আপনাকে আপনার.ucf এ বরাদ্দ করা উচিত:

পিন 1 = 29

পিন 2 = 51

পিন 3 = 32

পিন 4 = 41

পিন 5 = 34

পিন 6 = 35

পিন 7 = 40

পিন 8 = 33

পিন 9 = GND

পিন 10 = +ভি

প্রস্তাবিত:

জালপিক ওয়ান ডেভেলপমেন্ট বোর্ড: 5 টি ধাপ (ছবি সহ)

জালপিক ওয়ান ডেভেলপমেন্ট বোর্ড: যদি আপনি আমার নির্দেশাবলী প্রকল্পগুলি অনুসরণ করেন তবে আপনি জানেন যে আমি পিআইসি মাইক্রোকন্ট্রোলারের সংমিশ্রণে জেএএল প্রোগ্রামিং ভাষার একটি বড় ভক্ত। JAL হল একটি পাস্কালের মত প্রোগ্রামিং ভাষা যা মাইক্রোচিপের 8-বিট PIC মাইক্রোকন্ট্রোলারদের জন্য তৈরি করা হয়েছে। মো

একটি মাইক্রোকন্ট্রোলার ডেভেলপমেন্ট বোর্ড ডিজাইন করা: 14 টি ধাপ (ছবি সহ)

একটি মাইক্রোকন্ট্রোলার ডেভেলপমেন্ট বোর্ড ডিজাইন করা: আপনি কি পারফোর্ড প্রকল্প, ডিআইপি আইসি এবং হোম তৈরি পিসিবি থেকে বোর্ড হাউস এবং এসএমডি প্যাকেজিং দ্বারা গড়া মাল্টিলেয়ার পিসিবি থেকে উত্পাদন করতে আগ্রহী একজন নির্মাতা, শখের পাত্র বা হ্যাকার? তারপর এই নির্দেশযোগ্য আপনার জন্য! এই গুই

AVR ডেভেলপমেন্ট বোর্ড: 3 টি ধাপ

একটি AVR ডেভেলপমেন্ট বোর্ড: ইন্টারনেট Arduino এর সাথে প্রকল্পে পূর্ণ। কিছুক্ষণের জন্য ATMEGA328 মাইক্রোকন্ট্রোলারের তথ্য সমস্ত Arduino ডেটাতে অনুপস্থিত। এই ইন্সট্রাকটেবল AVR মাইক্রোকন্ট ব্যবহার করে কিভাবে প্রজেক্ট ডেভেলপ করা যায় তার শুরুটা পুনরুদ্ধার করতে চায়

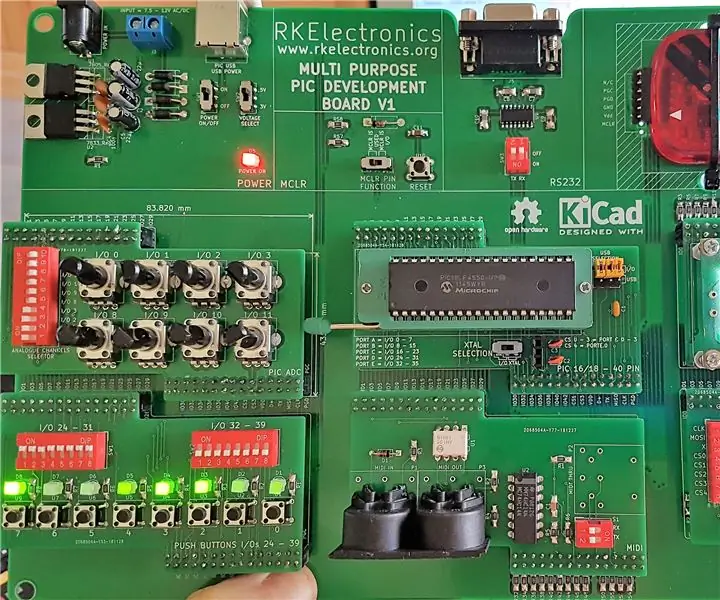

পিআইসি মাইক্রোকন্ট্রোলার ডেভেলপমেন্ট বোর্ড সিস্টেম: 3 ধাপ

পিআইসি মাইক্রোকন্ট্রোলার ডেভেলপমেন্ট বোর্ড সিস্টেম: এই প্রকল্পটি একটি পিআইসি ডেভেলপমেন্ট টুলের নকশা এবং ব্যবহারের জন্য, যা পিআইসি ভিত্তিক ইলেকট্রনিক প্রকল্পগুলির একটি বিস্তৃত পরিসরের জন্য নমনীয়। যা ব্যবহারকারী ভিত্তিক অনুমতি দেয়

WIDI - Zybo (Zynq ডেভেলপমেন্ট বোর্ড) ব্যবহার করে ওয়্যারলেস HDMI: 9 টি ধাপ (ছবি সহ)

WIDI - Zybo (Zynq ডেভেলপমেন্ট বোর্ড) ব্যবহার করে ওয়্যারলেস HDMI: আপনি কি কখনো ইচ্ছুক যে আপনি আপনার টিভিকে একটি পিসি বা ল্যাপটপের সাথে বাইরের মনিটর হিসেবে সংযুক্ত করতে পারেন, কিন্তু সেই সব বিরক্তিকর দড়িগুলোকে রাখতে চাননি? যদি তাই হয়, এই টিউটোরিয়ালটি শুধু আপনার জন্য! যদিও কিছু লক্ষ্য রয়েছে যা এই লক্ষ্য অর্জন করে, একটি