সুচিপত্র:

- লেখক John Day day@howwhatproduce.com.

- Public 2024-01-30 07:58.

- সর্বশেষ পরিবর্তিত 2025-01-23 14:36.

এই নির্দেশনায় আমরা SLG46855V তে 8-বিট এনালগ-টু-ডিজিটাল কনভার্টার (এডিসি) কীভাবে প্রয়োগ করতে হয় তা বর্ণনা করব যা I2C এর মাধ্যমে MCU দিয়ে লোড কারেন্ট এবং ইন্টারফেস বুঝতে পারে। এই নকশাটি বিভিন্ন বর্তমান সেন্সিং অ্যাপ্লিকেশন যেমন অ্যামিটার, ফল্ট ডিটেকশন সিস্টেম এবং ফুয়েল গেজের জন্য ব্যবহার করা যেতে পারে।

নীচে আমরা এডিসির বর্তমান অনুভূতি তৈরির জন্য সমাধান কীভাবে প্রোগ্রাম করা হয়েছে তা বোঝার জন্য প্রয়োজনীয় পদক্ষেপগুলি বর্ণনা করেছি। যাইহোক, যদি আপনি শুধু প্রোগ্রামিং এর ফলাফল পেতে চান, ইতিমধ্যে সম্পন্ন GreenPAK ডিজাইন ফাইল দেখতে GreenPAK সফটওয়্যারটি ডাউনলোড করুন। আপনার কম্পিউটারে গ্রিনপ্যাক ডেভেলপমেন্ট কিট লাগান এবং এডিসি কারেন্ট সেন্স তৈরি করতে প্রোগ্রাম হিট করুন।

ধাপ 1: এডিসি আর্কিটেকচার

ADC মূলত একটি এনালগ তুলনাকারী এবং একটি ডিজিটাল-টু-এনালগ কনভার্টার (DAC) নিয়ে গঠিত। তুলনাকারী ইনপুট ভোল্টেজ বনাম DAC আউটপুট ভোল্টেজ অনুভব করে, এবং পরবর্তীতে DAC ইনপুট কোড বাড়ানো বা কমানো নিয়ন্ত্রণ করে, যেমন DAC আউটপুট ইনপুট ভোল্টেজে রূপান্তরিত হয়। ফলে DAC ইনপুট কোডটি ADC ডিজিটাল আউটপুট কোডে পরিণত হয়।

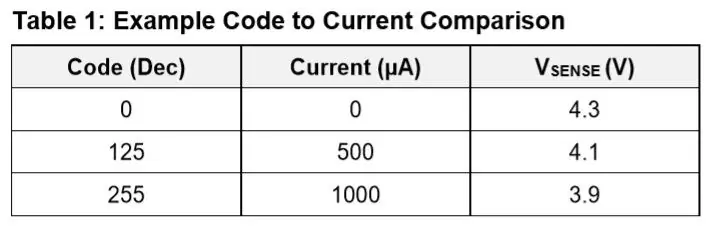

আমাদের বাস্তবায়নে, আমরা একটি পালস-প্রস্থ মডুলেশন (PWM) নিয়ন্ত্রিত প্রতিরোধক নেটওয়ার্ক ব্যবহার করে একটি DAC তৈরি করি। আমরা গ্রিনপাক ব্যবহার করে সহজেই ডিজিটালভাবে নিয়ন্ত্রিত PWM আউটপুট তৈরি করতে পারি। ফিল্টার করা হলে PWM আমাদের এনালগ ভোল্টেজ হয়ে যায় এবং এইভাবে একটি কার্যকর DAC হিসেবে কাজ করে। এই পদ্ধতির একটি স্বতন্ত্র সুবিধা হল যে ভোল্টেজগুলি সেট করা সহজ যা শূন্য কোড এবং পূর্ণ স্কেল (সমানভাবে অফসেট এবং লাভ) এর সাথে কেবল প্রতিরোধক মানগুলি সমন্বয় করে সেট করে। উদাহরণস্বরূপ, একজন ব্যবহারকারী একটি তাপমাত্রা সেন্সর থেকে আদর্শভাবে শূন্য কোড পড়তে চায় যার কোন বর্তমান (0 µA) 4.3 V এর সাথে সম্পর্কিত নয়, এবং 1000 µA এ 3.9 V (সারণি 1) এর সাথে পূর্ণ-স্কেল কোড। এটি কেবল কয়েকটি প্রতিরোধক মান নির্ধারণ করে সহজেই বাস্তবায়িত হয়। ADC পরিসীমা আগ্রহের সেন্সর পরিসরের সাথে মেলে, আমরা ADC রেজোলিউশনের সর্বাধিক ব্যবহার করি।

এই আর্কিটেকচারের জন্য একটি নকশা বিবেচনা হল যে একটি অভ্যন্তরীণ PWM ফ্রিকোয়েন্সি তার নিয়ন্ত্রণ লুপের অপ্রচলিত আচরণ প্রতিরোধ করার জন্য ADC আপডেট হারের চেয়ে অনেক দ্রুত হওয়া প্রয়োজন। অন্তত এটি ADC ডেটা কাউন্টার ঘড়ির চেয়ে 256 দ্বারা বিভক্ত হওয়া উচিত।

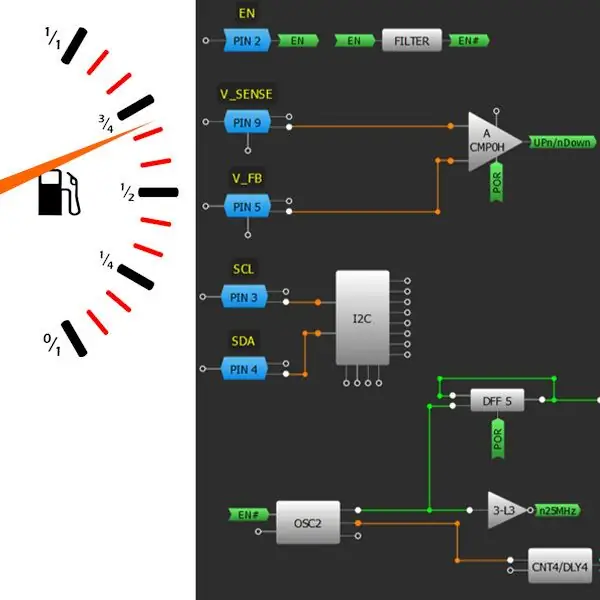

ধাপ 2: অভ্যন্তরীণ সার্কিট

নমনীয় ADC ডায়ালগ সেমিকন্ডাক্টর AN-1177 এ উপস্থাপিত নকশার উপর ভিত্তি করে। এডিসি কাউন্টার ঘড়ির জন্য ঘড়ির গতি 1 মেগাহার্টজ থেকে বাড়িয়ে 12.5 মেগাহার্টজ করা হয়েছে কারণ এসএলজি 46855 -তে 25 মেগাহার্টজ ঘড়ি পাওয়া যায়। এটি সূক্ষ্ম নমুনা রেজোলিউশনের জন্য অনেক দ্রুত আপডেট হার অনুমোদন করে। LUT ক্লকিং ADC ডেটা ঘড়ি পরিবর্তন করা হয়েছে তাই PWM DFF কম হলে এটি 12.5 MHz সিগন্যালের মধ্য দিয়ে যাবে।

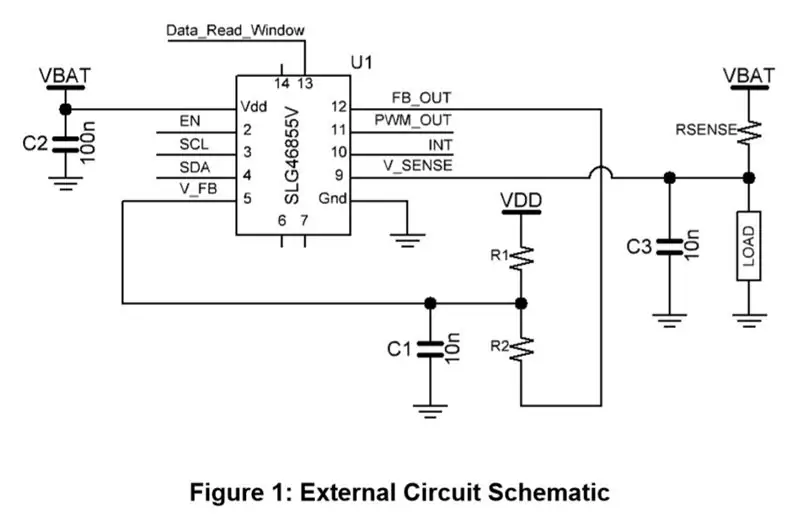

ধাপ 3: বাহ্যিক সার্কিট

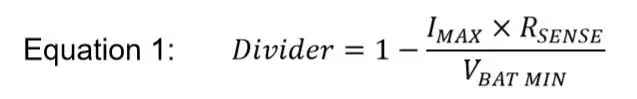

একটি বহিরাগত রোধকারী এবং ক্যাপাসিটরের নেটওয়ার্ক একটি PWM কে একটি এনালগ ভোল্টেজে রূপান্তর করতে ব্যবহৃত হয় যেমন চিত্র 1 -এ সার্কিট পরিকল্পিতভাবে দেখানো হয়েছে। এই নমনীয়তা অর্জনের জন্য, আমরা VDD এবং স্থল সমান্তরালে R1 এবং R2 প্রতিরোধক যোগ করি। একটি প্রতিরোধক বিভাজক VBAT কে ভোল্টেজ রেঞ্জের নিচের দিকে বিভক্ত করে। একটি প্রত্যাশিত ন্যূনতম VBAT এর বিভাজক অনুপাত সমীকরণ 1 ব্যবহার করে সমাধান করা যেতে পারে।

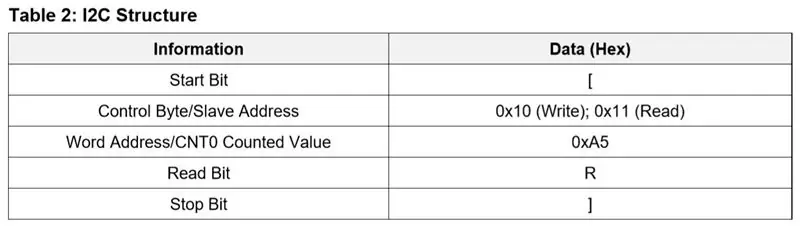

ধাপ 4: I2C নির্দেশাবলী পড়ুন

CNT0- এ সংরক্ষিত ডেটা ফিরে পেতে I2C কমান্ড স্ট্রাকচার বর্ণনা করে সারণি 1। I2C কমান্ডগুলির জন্য একটি স্টার্ট বিট, কন্ট্রোল বাইট, ওয়ার্ড অ্যাড্রেস, রিড বিট এবং স্টপ বিট প্রয়োজন।

একটি উদাহরণ I2C কমান্ড CNT0 গণনা মান ফিরে পড়ার জন্য নিচে লেখা আছে:

[0x10 0xA5] [0x11 R]

গণনা করা মান যা আবার পড়বে তা হবে ADC কোডের মান। উদাহরণস্বরূপ, ডায়ালগের ওয়েবসাইটে এই অ্যাপ্লিকেশন নোটের জিপ ফাইলে একটি Arduino কোড অন্তর্ভুক্ত করা হয়েছে।

ধাপ 5: ফলাফল

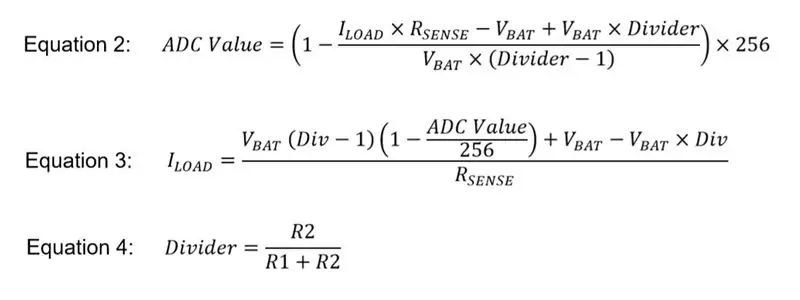

এডিসি কারেন্ট সেন্স ডিজাইনের যথার্থতা পরীক্ষা করার জন্য, প্রদত্ত লোড কারেন্ট এবং ভিডিডি লেভেলে মাপা মানগুলোকে তাত্ত্বিক মানের সাথে তুলনা করা হয়। তাত্ত্বিক ADC মান সমীকরণ 2 দিয়ে গণনা করা হয়েছিল।

ILOAD যা ADC মানের সাথে সম্পর্কযুক্ত তা 3 সমীকরণের সাথে পাওয়া যায়।

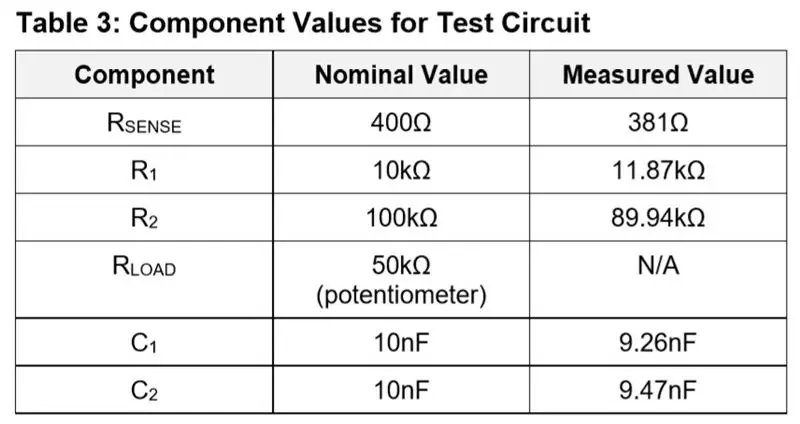

নিম্নলিখিত ফলাফলের জন্য আমি টেবিল 3 এ দেখানো এই কম্পোনেন্ট মান ব্যবহার করেছি।

ADL এর মান ILOAD রূপান্তরের রেজোলিউশনটি টেবিল 2 এ মাপা মানগুলির সাথে সমীকরণ 3 ব্যবহার করে এবং ADC এর মান 1 এ সেট করে গণনা করা যেতে পারে। 3.9 V এর VBAT সহ রেজোলিউশন 4.96 µA/div।

ADC কারেন্ট সেন্স সার্কিটকে সর্বোচ্চ 1100 µA এবং 381 Ω সেন্স রেসিস্টর সহ 3.6 V এর ন্যূনতম VDD লেভেলে অপ্টিমাইজ করার জন্য, আদর্শ বিভাজক সহগ 0.884 হবে, সমীকরণ 1 এর উপর ভিত্তি করে। 2, প্রকৃত বিভাজকের 0.876 এর বিভাজক সহগ রয়েছে। যেহেতু এটি কিছুটা কম, এটি একটি সামান্য বড় লোড বর্তমান পরিসরের অনুমতি দেবে যাতে ADC মানগুলি পূর্ণ পরিসরের কাছাকাছি থাকে কিন্তু উপচে পড়বে না। প্রকৃত বিভাজক মান 4 সমীকরণ দিয়ে গণনা করা হয়।

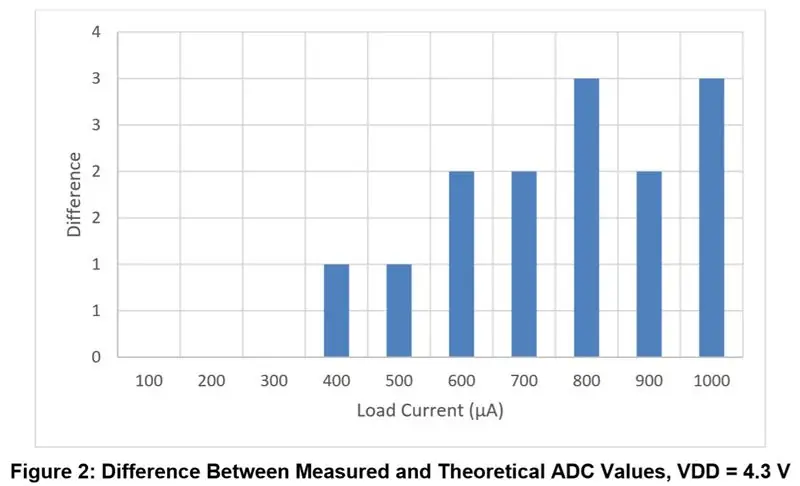

উপরে (পরিসংখ্যান 2-6, টেবিল 4-6) হল তিনটি ভোল্টেজ স্তরে সার্কিটের পরিমাপ: 4.3 V, 3.9 V, এবং 3.6 V। তাত্ত্বিক মানগুলি নিকটতম সম্পূর্ণ পূর্ণসংখ্যার গোলাকার। তিনটি ভোল্টেজ স্তরের পার্থক্যগুলি তুলনা করার জন্য একটি সারাংশ গ্রাফ রয়েছে। পরবর্তীতে বিভিন্ন ভোল্টেজ স্তরে তাত্ত্বিক এডিসি মান এবং লোড কারেন্টের মধ্যে পারস্পরিক সম্পর্ক প্রদর্শনকারী একটি গ্রাফ রয়েছে।

উপসংহার

ডিভাইসটি তিনটি ভোল্টেজ স্তরে পরীক্ষা করা হয়েছিল: 3.6 V, 3.9 V, এবং 4.3 V। তিনটি ভোল্টেজ স্তরের মধ্যে, এটি লক্ষ্য করা যায় যে ডিভাইসটি সাধারণত নির্বাচিত বাহ্যিক সার্কিটের জন্য 3.9 V এ আরও নির্ভুল ছিল। পরিমাপকৃত এবং তাত্ত্বিক ADC মানের মধ্যে পার্থক্য 700-1000 µA লোড স্রোতে মাত্র 1 দশমিক মান বন্ধ ছিল। প্রদত্ত ভোল্টেজ পরিসরে, পরিমাপকৃত ADC মানগুলি সবচেয়ে খারাপ ক্ষেত্রে নামমাত্র অবস্থার উপরে 3 দশমিক পয়েন্ট ছিল। বিভিন্ন VDD ভোল্টেজ স্তর অপ্টিমাইজ করার জন্য রোধকারী বিভাজকের আরও সমন্বয় করা যেতে পারে।

প্রস্তাবিত:

কিভাবে 8x8x8 LED কিউব তৈরি করবেন এবং এটিকে Arduino দিয়ে নিয়ন্ত্রণ করবেন: 7 টি ধাপ (ছবি সহ)

কিভাবে 8x8x8 এলইডি কিউব তৈরি করবেন এবং এটিকে আরডুইনো দিয়ে নিয়ন্ত্রণ করুন: জানুয়ারী 2020 সম্পাদনা: কেউ যদি ধারণা তৈরি করতে এটি ব্যবহার করতে চায় তবে আমি এটি ছেড়ে দিচ্ছি, কিন্তু এই নির্দেশাবলীর উপর ভিত্তি করে কিউব তৈরির আর কোন অর্থ নেই। LED ড্রাইভার ICs আর তৈরি করা হয় না, এবং উভয় স্কেচ পুরানো সংস্করণে লেখা হয়েছিল

কিভাবে ইভিএম মেশিন তৈরি করবেন ইলেকট্রনিক ভোটিং মেশিন (ইভিএম) কিভাবে তৈরি হয়: 3 টি ধাপ

কিভাবে ইভিএম মেশিন তৈরি করবেন ইলেকট্রনিক ভোটিং মেশিন (ইভিএম) কিভাবে তৈরি করা হয়: এটি কলেজ প্রকল্পের উদ্দেশ্যে ইভিএম মেশিনের প্রোটোটাইপ মোডাল। আপনি এই প্রকল্পটিকে প্রকল্প উপস্থাপনা, প্রকল্প প্রদর্শনী, মোডাল প্রেজেন্টেশন ইত্যাদি হিসাবে ব্যবহার করতে পারেন, এই প্রকল্পটি আপনাকে দ্রুত ওভারভিউ দেবে যে কিভাবে একটি ইভিএম মেশিন কাজ করে, এই প্রকল্প

কিভাবে ম্যাক টার্মিনাল ব্যবহার করবেন, এবং কিভাবে মূল ফাংশন ব্যবহার করবেন: 4 টি ধাপ

কিভাবে ম্যাক টার্মিনাল ব্যবহার করবেন, এবং কী ফাংশন কিভাবে ব্যবহার করবেন: আমরা আপনাকে দেখাব কিভাবে ম্যাক টার্মিনাল খুলতে হয়। আমরা আপনাকে টার্মিনালের মধ্যে কিছু বৈশিষ্ট্যও দেখাব, যেমন ifconfig, ডিরেক্টরি পরিবর্তন করা, ফাইলগুলি অ্যাক্সেস করা এবং arp। Ifconfig আপনাকে আপনার IP ঠিকানা এবং আপনার MAC বিজ্ঞাপন পরীক্ষা করার অনুমতি দেবে

আরডুইনো ন্যানো/মিনি কিভাবে তৈরি করবেন - কিভাবে বুটলোডার বার্ন করবেন: 5 টি ধাপ

আরডুইনো ন্যানো/মিনি কিভাবে তৈরি করবেন | কিভাবে বুটলোডার বার্ন করবেন: এই নির্দেশাবলীতে আমি আপনাকে দেখাব কিভাবে স্ক্র্যাচ থেকে একটি Arduino MINI তৈরি করতে হয়।

অটো লাইট সেন্স সহ গ্লাস মার্টিনি নাইট লাইট: 3 টি ধাপ

অটো লাইট সেন্স সহ গ্লাস মার্টিনি নাইট লাইট: একটি হালকা সেন্সিং এলইডি নাইট লাইটের একটি সহজ হ্যাক একটি সুন্দর রাতের আলো তৈরি করতে উপাদান: কাচের বোতল মার্টিনি গ্লাস সার্ভিং ট্রেব্রোকেন গ্লাস (বন্য দিকে হাঁটুন এবং এমন একটি জায়গা খুঁজুন যেখানে লোকেরা ঘন ঘন গাড়িতে প্রবেশ করে ) 3-6 LEDs (যদি আপনি চান