সুচিপত্র:

- লেখক John Day day@howwhatproduce.com.

- Public 2024-01-30 08:00.

- সর্বশেষ পরিবর্তিত 2025-01-23 14:36.

এই নির্দেশে, আমরা RTL এ একটি সাধারণ VGA কন্ট্রোলার ডিজাইন করতে যাচ্ছি। ভিজিএ কন্ট্রোলার হল ডিজিটাল সার্কিট যা ভিজিএ ডিসপ্লে চালানোর জন্য ডিজাইন করা হয়েছে। এটি ফ্রেম বাফার (ভিজিএ মেমরি) থেকে পড়ে যা প্রদর্শিত হওয়ার জন্য ফ্রেমকে প্রতিনিধিত্ব করে এবং প্রদর্শনীর উদ্দেশ্যে প্রয়োজনীয় ডেটা এবং সিঙ্ক সিগন্যাল তৈরি করে।

আপনি যদি ভেরিলগ/সিস্টেম ভেরিলগ কোড খুঁজছেন: ভেরিলগে আমার ব্লগ ভিজিএ কন্ট্রোলার এবং ভিডিও সিস্টেম দেখুন

ধাপ 1: একটি ভিজিএ কন্ট্রোলারের ইন্টারফেস

একটি ভিজিএ কন্ট্রোলারের প্রধান ইন্টারফেস সিগন্যালগুলি নিম্নরূপ

- পিক্সেল ক্লক বা ভিজিএ ক্লক

- HSYNC এবং VSYNC সংকেত

নির্বাচিত ভিজিএ ডিসপ্লের জন্য, আপনাকে প্রথমে পিক্সেল ক্লক চালানোর জন্য প্রয়োজনীয় ফ্রিকোয়েন্সি গণনা করতে হবে। এটি 3 টি পরামিতির উপর নির্ভর করে: মোট অনুভূমিক পিক্সেল, মোট উল্লম্ব পিক্সেল, স্ক্রিন রিফ্রেশ রেট।

সাধারণত, F = THP * TVP * রিফ্রেশ রেট

সংযুক্ত RAR- এ বিভিন্ন VGA প্রদর্শনীর জন্য প্রয়োজনীয় পিক্সেল ঘড়ির ডকুমেন্টেশন খুঁজুন।

HSYNC এবং VSYNC সংকেত পিক্সেল ঘড়ি থেকে উৎপন্ন হয়। HSYNC এবং VSYNC সংকেতগুলির সময়গুলি পরামিতি সংখ্যার উপর নির্ভর করে: অনুভূমিক এবং উল্লম্ব ফ্রন্টপোর্চ, অনুভূমিক এবং উল্লম্ব ব্যাকপোর্চ, অনুভূমিক এবং উল্লম্ব প্রদর্শন পিক্সেল, অনুভূমিক এবং উল্লম্ব সিঙ্ক পালস প্রস্থ এবং মেরু।

এই প্যারামিটারগুলি একটি নির্বাচিত ভিজিএ ডিসপ্লের জন্য মানসম্মত। সংযুক্ত RAR এ এই নথিগুলি খুঁজুন।

এই প্যারামিটারগুলি আমাদের ভিজিএ কন্ট্রোলার আইপি -তে কনফিগারযোগ্য প্যারামিটার।

ধাপ 2: ভিজিএ ডিসপ্লে সহ ভিজিএ কন্ট্রোলার সংহত করা

ভিজিএ ডিসপ্লের সাথে ভিজিএ কন্ট্রোলারকে কীভাবে সংহত করা যায় তা চিত্রটি দেখায়। সিস্টেমটি সম্পূর্ণ করতে আপনার আরও দুটি উপাদান প্রয়োজন:

- ফ্রেম বাফার: স্মৃতি যা ফ্রেমটি প্রদর্শন করার জন্য ধারণ করে।

- ভিডিও DAC: DAC যা RGB ডিজিটাল ডেটা রূপান্তর করে এবং উপযুক্ত ভোল্টেজ লেভেলে RGB এনালগ সিগন্যাল দিয়ে VGA ডিসপ্লে চালায়।

সহজ এবং জনপ্রিয় ভিডিও DAC গুলোর মধ্যে একটি হল ADV7125। এটি একটি 8-বিট DAC যা RGB ডিজিটাল শব্দগুলিকে 0-0.7 V এনালগ সংকেতে রূপান্তর করে এবং VGA ডিসপ্লে চালায়।

ধাপ 3: ফ্রেম বাফার ডিজাইন

এটি সেই স্মৃতি যা ছবিটি প্রদর্শনের জন্য 'সঞ্চয়' করে। এটি সাধারণত একটি র RAM্যাম বা কখনও কখনও রম। আমরা একটি চিত্র উপস্থাপন করার জন্য একটি ফ্রেম বাফার কিভাবে ডিজাইন করব তা নিয়ে আলোচনা করব। ফ্রেম বাফার এই ডিজিটাল তথ্যটি VGA কন্ট্রোলার থেকে কমান্ডে একটি ভিডিও DAC- এর কাছে প্রেরণ করে।

প্রথমে আমাদের পিক্সেলের গভীরতা ঠিক করতে হবে। এটি ছবির গুণমান নির্ধারণ করে, একটি পিক্সেল বিভিন্ন রঙের প্রতিনিধিত্ব করতে পারে। একটি 8-বিট DAC এর জন্য, আমাদের একটি পিক্সেলের প্রাথমিক রঙের উপাদানগুলি প্রতিনিধিত্ব করতে হবে: R, G, এবং B প্রতিটি 8 বিটে। এর মানে হল, একটি পিক্সেল 24-বিটের।

প্রতিটি পিক্সেল ফ্রেম বাফার মেমরি অবস্থানে একটি সংলগ্ন পদ্ধতিতে সংরক্ষণ করা হয়।

ধরুন একটি ছবি প্রদর্শিত হবে 800x600 পিক্সেল।

অতএব ফ্রেম বাফারের প্রয়োজন 800x600 = 480000 x 24 বিট মেমরি

মেমরির মোট আকার 800x600x24 = 1400 kB আনুমানিক।

যদি কালো এবং সাদা ছবি, 800x600x1 = 60 kB প্রায়।

ব্লক রs্যাম সম্ভবত Xilinx FPGAs- এ একটি ফ্রেম বাফারের প্রতিনিধিত্ব করতে ব্যবহৃত হয়।

ধাপ 4: নোট

- নির্বাচিত DAC এর উপর নির্ভর করে VGA কন্ট্রোলারে অতিরিক্ত সংকেত প্রয়োজন। আমি ADV7125 ব্যবহার করেছি।

- ভিজিএ ডিসপ্লে চালানোর আগে ভিএসওয়াইএনসি এবং এইচএসওয়াইএনসি-তে ফ্লিপ-ফ্লপের মাধ্যমে চক্র বিলম্ব যোগ করুন। এটি DAC এবং মেমরি বিলম্বের কারণে। পিক্সেল সিগন্যাল HSYNC এবং VSYNC এর সাথে সিঙ্ক্রোনাইজ করা উচিত। আমার ক্ষেত্রে, এটি 2 চক্র বিলম্ব ছিল।

- ব্লক র্যাম সাইজের সীমাবদ্ধতার কারণে যদি প্রদত্ত আকারের ফ্রেম বাফার FPGA তে ডিজাইন করা না যায়, তাহলে চিত্রের প্রতিনিধিত্ব করার জন্য ছোট মেমরি ব্যবহার করুন এবং সম্পূর্ণ ফ্রেমের সীমানার পরিবর্তে উপলব্ধ মেমরির সীমানায় ঠিকানাটি রোল করার জন্য কোডটি সম্পাদনা করুন। এটি পুরো স্ক্রিনে বার বার একই চিত্র প্রতিলিপি করবে। আরেকটি পদ্ধতি হল পিক্সেল স্কেলিং যাতে প্রতিটি পিক্সেল প্রতিলিপি করে পুরো চিত্রটি পূর্ণ পর্দায় দেখানো হয়, কম রেজোলিউশনে। কোডে অ্যাড্রেস ইনক্রিমেন্টেশন লজিক টুইক করে এটি করা যেতে পারে।

- আইপি সমস্ত FPGAs জুড়ে সম্পূর্ণরূপে বহনযোগ্য এবং Virtex-4 FPGA তে 100 MHz পর্যন্ত সময় যাচাই করা হয়।

ধাপ 5: সংযুক্ত ফাইল

RAR রয়েছে:

- ভিজিএ কন্ট্রোলার কোড

- ভিজিএ স্ট্যান্ডার্ডের পিডিএফ।

প্রস্তাবিত:

ভিএইচডিএলে একটি সহজ চার-উপায় সেট অ্যাসোসিয়েটিভ ক্যাশে কন্ট্রোলারের ডিজাইন: 4 টি ধাপ

ভিএইচডিএলে একটি সহজ চার-উপায় সেট অ্যাসোসিয়েটিভ ক্যাশে কন্ট্রোলারের ডিজাইন: আমার আগের নির্দেশে, আমরা দেখেছি কিভাবে একটি সহজ সরাসরি ম্যাপ করা ক্যাশে কন্ট্রোলার ডিজাইন করতে হয়। এবার আমরা এক ধাপ এগিয়ে গেলাম। আমরা একটি সহজ চার উপায় সেট সহযোগী ক্যাশে নিয়ামক ডিজাইন করা হবে। সুবিধা ? কম মিস রেট, কিন্তু পারফোর খরচে

ভিএইচডিএলে একটি প্রোগ্রামেবল ইন্টারাপ্ট কন্ট্রোলারের ডিজাইন: Ste টি ধাপ

ভিএইচডিএলে একটি প্রোগ্রামেবল ইন্টারাপ্ট কন্ট্রোলারের ডিজাইন: এই ব্লগে আমি যে ধরনের প্রতিক্রিয়া পাই তাতে আমি অভিভূত। আমার ব্লগে ভিজিট করার জন্য এবং আমাকে আপনার জ্ঞান শেয়ার করার জন্য অনুপ্রাণিত করার জন্য ধন্যবাদ বন্ধুরা। এবার, আমি আরেকটি আকর্ষণীয় মডিউলের নকশা উপস্থাপন করতে যাচ্ছি যা আমরা সমস্ত এসওসিতে দেখি - ইন্টারাপ্ট সি

ভিএইচডিএলে একটি সাধারণ ক্যাশে কন্ট্রোলারের ডিজাইন: 4 টি ধাপ

ভিএইচডিএলে একটি সাধারণ ক্যাশে কন্ট্রোলারের ডিজাইন: আমি এই নির্দেশযোগ্য লিখছি, কারণ আমি ক্যাশে কন্ট্রোলার শিখতে এবং ডিজাইন শুরু করার জন্য কিছু রেফারেন্স ভিএইচডিএল কোড পেতে একটু কষ্ট পেয়েছি। তাই আমি নিজে থেকেই একটি ক্যাশে কন্ট্রোলার ডিজাইন করেছি, এবং এটি FPGA তে সফলভাবে পরীক্ষা করেছি। আমার পি আছে

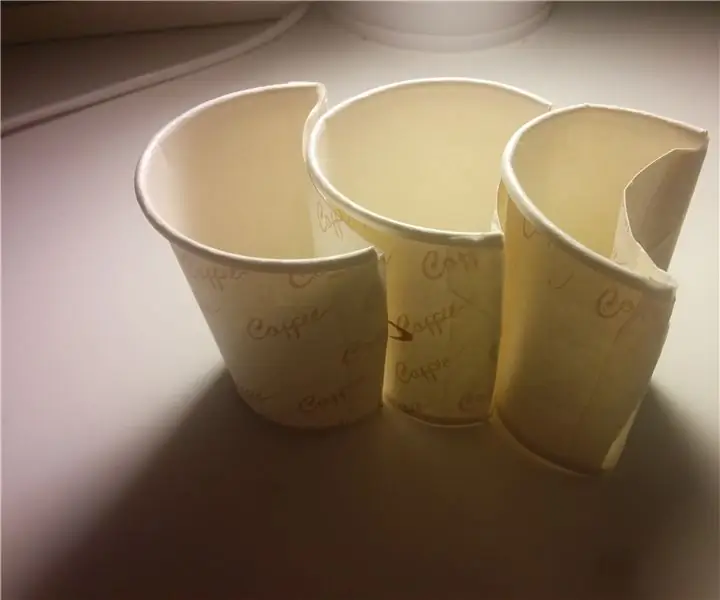

ডিজাইন থিংকিং পদ্ধতি দিয়ে একটি কার্ডবোর্ড কাপ ডিজাইন করুন: 7 টি ধাপ

ডিজাইন থিংকিং পদ্ধতি দিয়ে একটি কার্ডবোর্ড কাপ ডিজাইন করুন: হ্যালো, কার্ডবোর্ড কাপ যা ডিজাইন চিন্তা পদ্ধতি অনুযায়ী ডিজাইন করা হয়েছে, এখানে। এটি একবার দেখুন এবং একটি মন্তব্য করুন দয়া করে। আমি আপনার মন্তব্য দিয়ে আমার প্রকল্পের উন্নতি করবো :) অনেক ধন্যবাদ ---------------------------- মেরহাবা, ডিজাইন আমাকে ভাবছেন

একটি ব্যয়বহুল এবং ভারী পরিবর্ধক ছাড়া সাধারণ গৃহস্থালি বক্তাদের সাথে একটি আইপড বা অন্যান্য Mp3 প্লেয়ার সংযুক্ত করুন!: 4 টি পদক্ষেপ

একটি ব্যয়বহুল এবং ভারী পরিবর্ধক ছাড়া সাধারণ গৃহস্থালি স্পিকারগুলির সাথে একটি আইপড বা অন্যান্য এমপি 3 প্লেয়ার সংযোগ করুন! এই নির্দেশনায় আমি আপনাকে দেখাব কিভাবে আপনি তাদের যেকোনো Mp3 প্লেয়ার বা সাউন্ড পোর্টের সাথে যেকোনো ডিভাইসের সাথে সংযুক্ত করতে পারেন